# Analysis of Interface Trap Density between Semiconductor-Gate insulator with C-V characteristics

Seung-Hyeon Jeong\*, Se-Min Kim and Chung-Kun Song

Dept. of Electronics engineering, Dong-A University,

840, Hadan-dong, Saha-Gu, Busan, Korea

TEL:82-51-200-7711, e-mail: cksong@dau.ac.kr

Keywords: Interface Trap density, pentacene, C-V characteristics

### **Abstract**

In this paper, we analyzed interface trap density between pentacene and PVP and SiO2 gate dielectric by using high-low C-V characteristics. The interface trap density was  $10^{13}$  cm<sup>-2</sup>eV<sup>-1</sup>.

# 1. Introduction

The OTFTs are attracted much attention because of their potential applications to flexible devices such as flexible displays, plastic logic circuits, and organic RFIDs [1-2]. However, the interface charge properties between organic semiconductor and organic gate insulator, which are important to performances such as mobility, threshold voltage, sub-threshold slope, are not evidently identified yet.

In this paper, we applied the combined high-low frequency capacitance-voltage characteristics to analyze the interface trap density between pentacene and gate insulators such as SiO<sub>2</sub> and poly-4-vinylphenol (PVP).

## 2. Experimental

We fabricated two types of capacitors consisting of metal-insulator-semiconductor-metal (MISM) structure. One capacitor used  $p^+$ -Si substrate for gate electrode,  $SiO_2$  which has 300Å thickness for gate insulator, pentacene for semiconductor and Au for top electrode. The other capacitor used Al for gate electrode on glass substrate, PVP for gate insulator using the spin-coating, pentacene for semiconductor and Au for electrode.

We used E4980A LCR meter of Agilent to measure the capacitance-voltage characteristics with various frequency of small signal in dark atmosphere to avoid degradation due to the light [3]. When we measured capacitances, we gave the delay time. The interface traps density was extracted by eq. 1 [4].

$$D_{it} = \frac{C_{Ins}}{q} \left[ \left( \frac{1}{\Delta C/C_{Ins} + C_{HF}/C_{Ins}} - 1 \right)^{-1} - \left( \frac{1}{C_{HF}/C_{Ins}} - 1 \right)^{-1} \right]$$

(1)

Where  $\Delta C = C_{LF} - C_{HF}$ ,  $C_{Ins}$  is the capacitance of gate insulator,  $C_{LF}$  is the capacitance at the low frequency and  $C_{HF}$  is the capacitance at the high frequency.

#### 3. Results and discussion

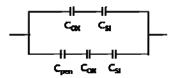

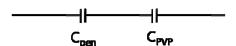

First, the equivalent circuit of MISM with  $SiO_2$  insulator is shown in Fig. 1. The MISM with  $SiO_2$  insulator has the parasitic capacitances caused by  $SiO_2$  ( $C_{OX}$ ) and  $p^+$ -Si ( $C_{Si}$ ) substrate. Therefore, the measured C-V curves should be modified by eliminating the parasitic capacitances.

Fig. 1. The equivalent circuit of SiO<sub>2</sub> capacitor.

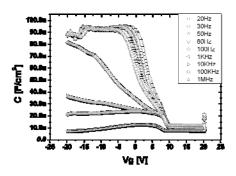

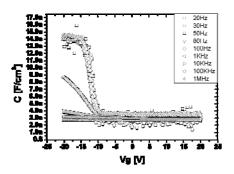

As shown in Fig. 2, the C-V curves were measured with various frequencies from 20Hz to 1MHz. The C-V curves were reduced to the minimum capacitance in the positive voltage where pentacene layer was totally depleted, and they were rose to the maximum capacitance of 90 nF/cm<sup>2</sup>. The threshold voltage was about 10V, indicating the negative fixed interface charge density of -9x10<sup>-7</sup> Coul/ cm<sup>2</sup>.

Fig. 2. The C-V curves with the various frequencies of  $SiO_2$  capacitor.

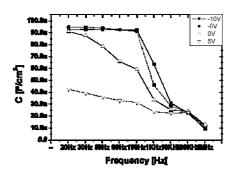

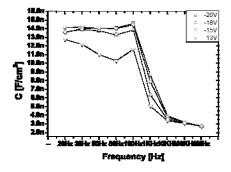

As the frequency increased, C-V curves were smeared out because the interface traps could not respond to high frequency [5]. The relaxation frequency was about 1KHz as shown in Fig. 3.

Fig. 3. The frequency dependence of SiO<sub>2</sub> capacitor.

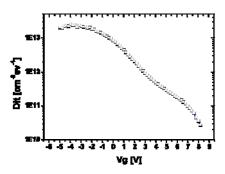

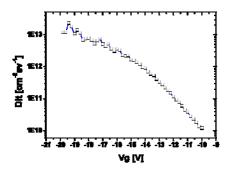

The interface trap density was extracted from the low C-V at 20Hz and the high C-V at 1KHz, and depicted in Fig. 4. The interface trap density was varied from  $10^{13}~\text{cm}^{-2}\text{eV}^{-1}$  to  $10^{10}~\text{cm}^{-2}\text{eV}^{-1}$  as the Fermi energy level moved along the band gap.

Fig. 4. The interface trap density of SiO<sub>2</sub> capacitor.

MISM with PVP capacitor exhibited the simple equivalent circuit as shown in Fig. 5. So that it did not need modification as done in MISM with  $SiO_2$  capacitor.

Fig. 5. The equivalent circuit of PVP capacitor.

The C-V curves also exhibited the smeared-out phenomena as  $SiO_2$  capacitor, representing the existence of interface trap as shown in Fig. 6.

Fig. 6. The C-V curves with the various frequencies of PVP capacitor.

The threshold voltage was -10V, indication the positive fixed interface charge of +9x10-7 Coul/ cm<sup>2</sup>, which was different from SiO<sub>2</sub> insulator. The relaxation frequency was about 1KHz similar to that SiO<sub>2</sub> as shown in Fig. 7, implying the relaxation frequency is related to pentacene.

Fig. 7. The frequency dependence of PVP capacitor.

The interface trap density was very similar to SiO2 varied from 10<sup>13</sup> cm<sup>-2</sup>eV<sup>-1</sup> to 10<sup>10</sup> cm<sup>-2</sup>eV<sup>-1</sup> as shown in Fig. 8, indicating that the interface traps density was attributed pentacene near interface, being independent from insulators.

Fig. 8. The interface trap density of PVP capacitor.

# 4. Summary

We fabricated two types of MISM capacitors with the same pentacene and the different insulators such as SiO<sub>2</sub> and PVP insulator, respectively. The fixed interface trap charge was different depending on insulator; the positive charge for PVP and the negative for SiO<sub>2</sub>. However, the interface trap density exhibited the same variation from 10<sup>13</sup> cm<sup>-2</sup> to 10<sup>10</sup> cm<sup>-2</sup> independent from insulator, indicating that the interface trap was attributed to pentacene near interface.

# 5. Acknowledgements

This research was supported by a grant(F004061) from Information Display R&D Program funded by the Ministry of Knowledge Economy of Korean government.

## 6. References

- 1. Z. Bao, et al., Chem. Mater., 9, p.1601, (2001).

- 2. T. Kawase, et al., Adv. Mater., 9, p. 1299, (1997).

- 3. Cipolloni S., et al., Thin solid films, 515, p. 7546 (2007).

- 4. E. H. Nicollian, et al., "MOS (Metal Oxide Semiconductor) Physics and Technology", John Wiley, New York, (1982).

- 5. Yi-Ming Chen, et al., Solid-state electronics, 52, p.269, (2008).