# Multi 출력단을 Single Transformer 로 통합 설계한 고효율 PDP 용 전원시스템

박상갑\*, 노정욱\*, 한상규\*, 홍성수\*, 사공석진\*, 김종해\*\* 이효범\*\* \*국민대학교 전력전자연구소, \*\*삼성전기(주) P&M사업부

# A High efficiency Multi output PDP Power system with Single transformer structure

Sang-Gab Park<sup>\*</sup>, Chung-Wook Roh<sup>\*</sup>, Sang-Kyu Han<sup>\*</sup>, Sung-Soo Hong<sup>\*</sup>, Sug-Chin Sakong<sup>\*</sup>, Jong-Hae Kim<sup>\*\*</sup>, Hyo-Bum Lee<sup>\*\*</sup>

\*Kookmin Univ. Power Electronics Center, \*\*Samsung Electro-Machanics CO., LTD

## **ABSTRACT**

기존 PDP 전원 시스템은 일반적으로 두 개의 절연형 Transformer 를 사용하여 유지전원( $V_s$ )과 어드레스 전원( $V_A$ ), Multi단 전원( $V_M$ ) 으로 구성된다. 이들 각 전력 변환 회로에 Transformer 및 제어 IC 가 사용되므로, 효율 저감 및 원가 상 숭, 소자 스트레스 등의 단점을 가지고 있다.

본 논문에서는 절연형 Transformer 한 개로 PDP 전원시스템을 구동하는 방식에 대해 제안한다. 제안된 방식은 DC/DC 전력단의 고효율 동작 및 신뢰성 개선은 물론 부피, 크기를 줄여 원가 저감에 기여한다. 또한, 제안된 방식은 PDP 구동 방식의 하나인 Address Display Separation Method (ADSM) 에 적합하다. 기존 방식과 제안된 방식을 비교하고 이론적 분석과실험을 통해 제안된 방식의 우수성을 확인 하였다.

# 1. 서 론

최근 평면 디스플레이의 기술이 발전하면서 디스플레이 장치들이 대형화 되어가고 있는 추세에 있다. 특히, PDP TV 는 큰 화면 사이즈와 얇은 두께, 그리고 넓은 시야각 등의 이점을 가지고 있기 때문에 평판 디스플레이 (Flat Panel display) 시장에서 각광을 받고 있다. PDP TV 의 경우 이러한 대형화 추세에 맞춰 제품의 크기 및 무게저감 그리고 높은 전력밀도와효율 특성을 요구하고 있다.

PDP 의 동작은 Reset, Addressing, Sustaining 의 세 가지 구간으로 구성되어 있고 PDP 패널 특성 상, 서스테인 전원( $V_s$ ) 단의 경우 높은 전력을 소비하며 Load Profile 에 따른 높은 효율을 가져야 하는 제약이 있다. 더구나 화면의 계조를 표현하기 위해, Address Display Separation Method (ADSM) 방식을 채택하는 PDP 의 경우, 서스테인 전원( $V_s$ ) 단과 어드레스 전원( $V_A$ ) 단의 부하는 16.67ms(60Hz) 주기로 무부하에서 과부하를 반복하는 맥동성의 부하 조건을 가진다.

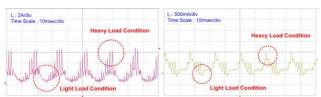

(a) 서스테인 출력전류 파형 (b) 어드레스 출력전류 파형 그림 1 서스테인 전원(Vs), 어드레스 전원(Vs) 단의 출력전류 파형

그림 1 은 50"급 Samsung HD PDP 의 서스테인 전원단 과어드레스 전원단의 출력 전류 파형를 나타낸다. 이 그림을 통해 알 수 있듯이 전류가 맥동하기 때문에 전류가 클 때는 스위치의 ZVS 가 잘 되지만 전류가 적을 때는 ZVS 를 보장할 수없다. 이러한 부하 동특성으로 인해 Vs 단과 Va 단의 최적의전압 제어가 어렵고, 동작 주파수나 동작 시비율 변화가 심해, 전력 변환 효율 저감 및 신뢰성 저감이 야기된다.

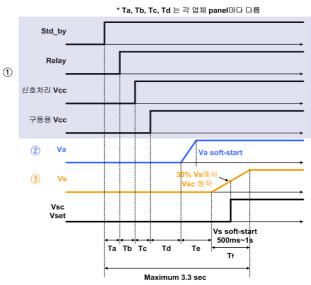

또한, PDP 의 경우 발광원리상 방전 시 매우 큰 서지성 전류가 흐르게 되므로 서스테인과 어드레스 전원 및 구동보드에 다수의 큰 캐패시터가 병렬로 부가되어야 한다. PDP의 구동모듈은 수많은 전국에 각각의 필요 전원을 고속 스위칭하며 공급하기 때문에 대부분이 반도체를 이용한 스위칭 소자로 구성되어 있다. 이에 따라 스위칭 소자를 보호하고 초기의 전원 인가시 이상 방전 및 화질 문제를 예방하기 위해서는 반드시 그림 2 의 전원 투입 순서를 지켜야 한다. 따라서, ① 저전압 계통 (신호처리 및 구동용  $V_{CC}$ ), ② 어드레스 계통( $V_A$ ), ③ 서스테인 계통( $V_S$ )의 순으로 전원을 인가하고, 그 역순으로 전원을 제거하는 것이 일반적이다.

그림 2 Power on time sequence (50"급 Samsung PDP 기준)

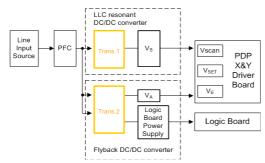

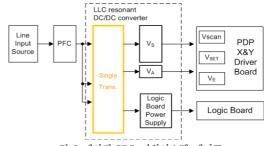

그림 3 는 두개의  $Transformer(T_1,T_2)$  를 사용하는 기존 PDP 전원시스템 개념도를 나타낸다.

그림 3 기존 PDP 전원시스템 개념도

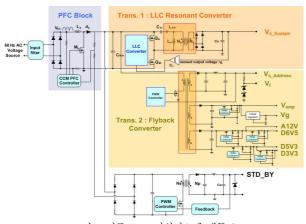

그림 4 는 기존 전원시스템의 계통도로서, 기존은 Two-stage 구동방식으로 입력전류의 Harmonic 을 줄이기 위한 PFC 단과 출력전압을 안정적으로 유지를 해주는 DC/DC 컨버터단으로 2단 직렬 구조를 가진다. 그리고 PFC 단은 역률개선 성능에 있어 우수한 특성을 보이는 부스트 토폴로지 (Boost Topology) 를 채택하고, 다수의 DC/DC 단은 입력과 출력사이에 전기적인 절연을 위해 두 개의 트랜스포머(T1, T2) 가 사용된 절연형 컨버터이다. 이때 서스테인 전원(Vs) 을 공급하기 위한 DC/DC 단은 높은 전력밀도 및 효율특성을 보이는 LLC 공진형 컨버터이고 어드레스 전원(VA) 및 다수의 저전원(VM) 을 공급하기 위한 DC/DC 단은 플라이백(Flyback) 컨버터를 사용한다. 여기에 다수의 안정적인 저전원(VM) 을 공급하기 위해 강압형 컨버터인 벅(Buck) 컨버터를 사용하고 있다.

그림 4 기존 PDP 전원시스템 개통도

본 논문에서는 PDP 전원회로를 구성하는 각 컨버터의 최적 Topology 에 관한 연구와 서스테인과 어드레스 전원 등 여러가지 전원들을 시스템적인 측면에서의 상호배열 및 계통에 대한 연구 결과로, PDP 구동에 필요한 모든 전원을 하나의 Transformer 로 통합 설계한 Single Transformer 구조의 PDP 전원시스템을 제안하였다.

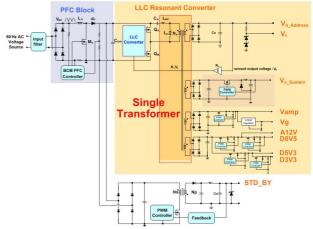

# 2. 제안된 전원시스템

기존 방식인 서스테인 전원( $V_s$ ) 과 어드레스 전원( $V_A$ ), Multi 단 전원( $V_M$ ) 을 공급하는 DC/DC 컨버터 각각의 트랜스포머 ( $T_1$ ,  $T_2$ ) 를 그림 5, 6 과 같이 PDP 구동에 필요한 Multi 출력 단을 Single Transformer 로 통합 설계한 새로운 PDP 전원시스템 개념도 및 계통도을 나타낸다. 제안된 전원시스템은 주 궤환 전압제어 부분이 어드레스 전원( $V_A$ ) 에서 이루어지고, 별도의 Post Regulator 들을 사용하여  $V_s$  전원과 그 외 PDP 구동에 필요한 다중 전원들을 공급하는 구조로 되어 있다.

그림 5 제안된 PDP 전원시스템 개념도

그림 6 Multi 출력단을 Single Transformer로 통합 설계한 50" F\_HD PDP 전원시스템의 계통도

제안된 방식은 상용 라인 입력 전원으로부터  $90\sim264 Vrms$ 의 입력을 받아 고조파 규제 회피를 위한 PFC (Power Factor Correction) 단를 통해 부스트-업(boost-up) 되어 약  $370\sim400 V_{DC}$  직류 전압을 출력하며 이로부터 다수의 DC/DC 컨버터를 거쳐 PDP 구동에 필요한 다양한 전원들을 공급한다.

먼저, 역률 개선을 수행하는 PFC 가 PDP 용 SMPS 의 가장 앞 단에 위치하며 PFC 성능에 있어 우수한 특성을 보이는 부스트 토폴로지(Boost Topology) 를 채택하고 DC/DC 단은 효율 및 출력전압의 Regulation 특성이 우수한 LLC 공진형 컨버터 사용한다 $^{[1][2]}$ . 그리고 강압형 컨버터를 사용하여 서스테인 전원( $V_S$ ) 과 그 외 PDP 구동에 필요한 다수의 저전원( $V_M$ ) 을 발생시키는 구조로 되어 있다. 다양한 전원을 공급하는 DC/DC 단을 하나의 Transformer 로 통합 설계하여도 전원인가순서를 만족시킬 수 있는 장점을 가진다.

또한 제안된 방식은 기존 방식에 비해 DC/DC 단 출력 전압을 제어하는 제어기수가 적어지고, 부가적인 반도체 스위칭손실을 줄 수 있다. 서스테인 전원(Vs) 단과 어드레스 전원(VA) 단이 맥동성의 부하로 동작할 때 기존 방식은 출력 부하 동특성에 따라 1차측 공진 전류가 맥동하지만 제안된 방식은 그림 8(b) 와 같이 부하 동특성의 의해서도 1차측 공진 전류가 일정하게 흐르는 것을 볼 수 있다.

이러한 특성으로, PDP 전원의 최적 전압 제어가 용이하고, 동작 주파수 변화가 덜해, 궁극적으로 전력 변환 효율 및 신뢰 성을 향상시킬 수 있다. 그리고 각 Block 의 Transformer 와 부품수를 줄일 수 있으며, 또한 부품이 차지하는 공간을 절약 할 수 있으므로 PCB 의 경량화는 물론 PDP 전원회로의 제조 원가를 저감할 수 있는 이점들을 가지고 있다.

# 3. 실험 결과

제안된 전원시스템의 타당성을 입증하기 위해 50"급  $F_{HD}$  PDP 전원 Prototype 을 제작하여 실험하였다. 표 1 에 실험을 위한 조건을 나타내었다.

표 1 50"급 F\_HD PDP 전원시스템 사양

| Condition      | Value                                                                                                                                                        |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Input Voltage  | AC90 ~ 264Vrms                                                                                                                                               |  |  |

| Output Power   | 600W                                                                                                                                                         |  |  |

| Output Voltage | V <sub>A</sub> _60V, V <sub>S</sub> _210V, V <sub>m1</sub> (V <sub>g</sub> , D12, V <sub>amp</sub> )<br>V <sub>m2</sub> (D3.4, D5.3, V <sub>t</sub> ), ST_BY |  |  |

| Output Current | V <sub>A</sub> _2A, V <sub>S</sub> _1.6A, V <sub>g</sub> _1.0A, V12_2.0A, V <sub>amp</sub> _2.5A<br>D3.4_3.0A, D5.3_3.5A, Vt_0.01A, ST_BY_1.0A               |  |  |

제안된 전원시스템에 사용한 다중 출력 LLC 공진형 컨버터에서 자화 인덕턴스와 공진 인덕턴스의 비율(k)에 따라 얻은최대 이득(M),  $Z_r$ 과 주어진 공진 주파수( $\omega_r$ )을 이용하여 공진인덕턴스, 공진 커페시턴스 및 자화 인덕턴스를 구할 수 있다<sup>[3]</sup>. Single Transformer 는 Section Bobbin 구조를 사용하였다.

표 2 는 LLC 공진 탱크 설계를 위한 각부 설계 사양 및 Single Trans. 사양을 나타낸다.

표 2 LLC 공진 탱크 설계 사양 및 Single Trans. 사양

| Design parameters       | Value                                                                                            |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------|--|--|

| Magnetic inductor       | 520uH                                                                                            |  |  |

| Resonant capacitor      | 30nF                                                                                             |  |  |

| Resonant inductor       | 220uF                                                                                            |  |  |

| Maximum switching freq. | 65kHz                                                                                            |  |  |

| Trans. turn ratio       | N <sub>p</sub> :N <sub>s1</sub> :N <sub>s2</sub> :N <sub>s3</sub> :N <sub>s4</sub> =47:12:54:4:3 |  |  |

| Trans. Size             | EER6062_Section Bobbin                                                                           |  |  |

| Effective Core Volume   | 51.63 [cm <sup>3</sup> ]                                                                         |  |  |

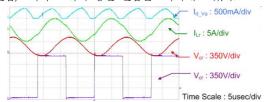

그림 7 은 제안된 전원시스템의 전자 부하 동작파형으로 위에서부터 2차측  $V_A$  추력 전류, 1차측 공진 전류, 공진 Cap. 양단 전압, 1차측 스위치 양단 전압을 나타내고 있다.

그림 7 제안된 전원시스템의 각부 동작 파형

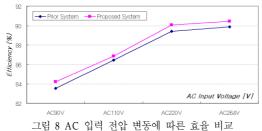

그림 8 은 기존 방식과 제안된 전원시스템의 효율을 AC 입력 전압 변동에 따른 그래프를 나타내었다. 예상한대로 제안된 방식의 도통 손실이 작기 때문에 기본 방식대비 효율이 더 높아짐을 확인하였다.

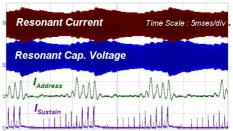

그림 9. 제안된 전원시스템을 적용한 50"급  $F_{HD}$  PDP Panel 에 실장 한 동작 파형이다. 위에서부터 1차측 공진 전류  $(I_{Lr})$ , 공진 Cap. 양단 전압 $(V_{Cr})$ , 서스테인 전류 $(I_S)$ , 어드레스 전류 $(I_A)$  파형을 나타내고 있다.

표 3 은 기존과 제안된 전원시스템의 부품수, 원가, 무게를 비교하여 보았다. 하나의 절연형 트랜스포머를 사용함으로서,

그림 9 제안된 전원시스템의 50"급 F\_HD PDP Panel 실장 파형

기존보다 부품이 차지하는 공간을 줄일 수 있으며, 이로 인해 PDP 전원시스템의 전체 크기 및 부피의 감소로 제조원가 또한 저감할 수 있는 효과를 얻을 수 있다.

표 3 기존과 제안된 전원시스템의 부품수, 원가, 무게 비교

| 기존 전원시스템 (EA, \$) |      |      | 제안 전원시스템 (EA, \$) |      |      |

|-------------------|------|------|-------------------|------|------|

| 부품수               | 원가   | 무게   | 부품수               | 원가   | 무게   |

| 439               | 30.8 | 1749 | 419               | 29.3 | 1623 |

그림 10 는 기존 방식과 제안된 방식의 50"급 F\_HD PDP 전원 시제품 비교 사진이다. 기존 대비 Transformer 가 한 개로 줄고 그에 따른 제어단도 간단해진다. 또한 시제품을 전체적으로 보면 부피가 줄어들었음을 알 수 있고 실질적으로 PCB 크기 및 공간 활용이 용이함을 알 수 있다.

(a) 기존 방식(Two Trans.) (b) 제안 방식(Single Trans.) 그림 10 기존 및 제안된 방식의 50"급 PDP 시제품

### 4. 결 론

본 논문에서는 50"급 F\_HD PDP 용 전원을 위한 새로운 전 원시스템을 제안하였다. 하나의 절연형 Transformer 를 적용함으로서, 기존 방식에 비해 DC/DC 단 출력 전압을 제어하는 제어기수가 적어지고 PDP 전원의 최적 전압 제어가 용이하며, 또한, 전력 변환 효율 및 신뢰성을 향상시킬 수 있음을 실험을통해 확인하였다. 그리고 부품이 차지하는 공간을 줄임으로서, PDP 전원시스템의 전체 크기와 부피를 줄일 수 있을 뿐 아니라, 제조원가 또한 저감할 수 있는 전원시스템임을 확인하였다.

이 논문은 삼성전기의 연구비 지원에 의하여 연구되었습니다.

### 참 고 문 헌

- [1] Bo Yang, yuancheng Ren, Fred C. Lee, "Integrated magnetic for LLC resonant converter" IEEE APEC 2002. Seventeenth Annual IEEE, 2002 vol.1, pp. 345-351

- [2] Bo Yang, Fred C. Lee, Alpha J.Zhang and Guisong Huang, "LLC resonant converter for front end DC/DC conversion" IEEE APEC 2002 Vol.2, pp. 1108- 1112

- [3] Won-seok Nam, Sang-kyu Han, Chung-wook Roh Sung-soo Hong, "Steady-state analysis of LLC resonant converter for optimum design" 전력전자학회, pp. 375-377