# 디지털 회로 검증을 위한 하드웨어 시뮬레이션 시스템 구현에 관한 연구

조 현 섭, 오 명 관\* 청운대학교 디지털방송공학과, \*혜전대학교 컴퓨터학과 e-mail: chohs@chungwoon.ac.kr

# Study on Implementation of Hardware Simulation System for Verification of Digital Circuit

Hyun-Seob Cho, Myoung-Kwan Oh\*

Dept of Digital Broadcast Engineering Chungwoon University

\*Dept of Computer Science Hyejeon College

Abstract - According to the development of VLSI integration technology and getting bigger the circuit size, it is a significant problem to verify systemized circuit. The faster and more accurate verification has very significant meaning in the field of electronic industry because it can yield the product comparably faster and reduce the trial and errors. In spite of the presence of various kind of Integrated Circuits it's not always easy to get the right part. Besides, it is hard to find a vendor for a small quantity consumers like who develop prototype applications. In this study, we've tried to get the logical signals from the PC based device we've developed that correspondents with the real ICs. It can emulate decoder ICs, multiplexers, demultiplexers and basic logic gates.

# 1. 서 론

최근 공정기술이 발달함에 따라 회로의 규모가 커 점에 따라 설계된 회로의 검증 문제가 중요한 과제로 대두되었다. 보다 빠르고 정확한 검증은 일각을 다투는 전자 산업의 시장에서 상대적으로 신속하게제품을 생산할 수 있고, 제품생산까지의 시행착오를 줄여줄 수 있기 때문에 상당히 중요한 의미를 갖는다. 본 논문은 이러한 문제점을 해결하기 위한 유연성 있는 신호처리 방법으로 DIGITAL LOGIC을 컴퓨터 논리연산 명령으로 구성하여 외부에서의 입력신호에 대응하는 논리연산의 결과를 입・출력 채널을 통해 외부로 출력해 줄 수 있는 DEVICE에 관한 연구이다. 이는 DECODER IC, MULTIPLEXER & DEMULTI PLEXER, 기본 LOGIC IC 등의 가상구현 및 BIT출력이 가능한 DIGITAL 신호원으로서의 기능이 가능하게 하였다.

### 2. 회로 구성 및 동작

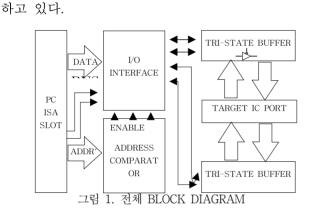

본 논문에서 언급되어지는 DIGITAL LOGIC의 가상 구현을 위하여 그림1의 BLOCK DIAGRAM으로 구성된 회로가 사용되어 진다. 전체 회로는 크게 두개의 부분으로 설명되어질 수 있는데 첫째, 컴퓨터와의 입·출력을 행하는 8BIT 크기의 9 CHANNEL I/O INTERFACE 부분과 둘째, 입·출력의 방향 및전원 핀의 설정을 위한 TRI-STATE BUFFER BOARD이다.

# 2.1.1 9 CHANNEL 8BIT I/O INTERFACE

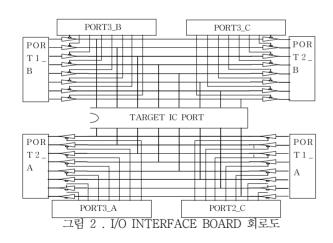

범용 입·출력 인터페이스 소자인 8255A를 사용하였으며 ADDRESS COMPARATOR 74LS688에 의하여 ADDRESS 200H부터 20BH 까지 프로그래밍 할 수 있게 하였다. (그림2 참조) 8255A는 모드0를 사용하여 TRI-STATE BUFFER BOARD에 TARGET IC의 입·출력 방향신호와 컴퓨터 프로그

램으로 구현한 논리 관계식에 따라 입·출력 데이터 신호를 전송한다.

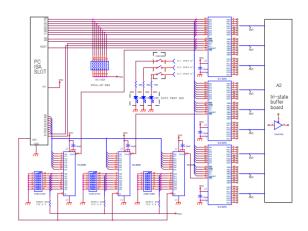

#### 2.1.2 TRI-STATE BUFFER BOARD

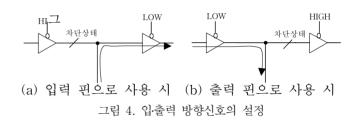

그림3은 TRI-STATE BUFFER BOARD의 전체 회로로서 8255A로부터 입·출력 방향신호를 받아 논리레벨이 HIGH(+5V)일 때에는 TRI-STATE BUFFER 출력을 HIGH IMPEDANCE 상태로 두고, LOW(0V)일 때에는 도통상태에 두어 입력과 출력 선을 분리시킨다. 이때 한 LINE에 연결된 두 개의 TRI-STATE BUFFER IC는 동시에 도통되지 않게 프로그램 되어진다. 그림 4에서는 한 개의 핀에 대한 입력 및 출력 설정 시 각각의 상태를 보여준다. 부가적으로 각 핀마다 PULL-UP 저항을 두어 OPEN -COLLECTOR 형태의 IC를 지원해주며 입·출력선 각각 전류제한 저항을 두어 회로를 보호

# 2.2. Software 구성

Software의 구성은 크게 두 가지로 살펴볼 수 있는데 각각의 IC에 대한 정보를 가지고 있는 DATA FILE과 이를 호출하여 실행하는 FILE로 나눌 수 있다.

그림 3. TRI-STATE BUFFER BOARD 회로도

### 2.2.1 DATA FILE

DATA FILE에는 TARGET IC의 논리적 기능과입·출력 핀의 방향을 제어하기 위한 제어문자, 전원 핀의 번호, 전체 핀 수 등이 기술되어진다. 위의기술 사항들은 16진수로 표현되며 TEXT FILE로저장된다.

# 2.2.2 실행 FILE

실행 FILE에서는 DATA FILE에서 기술된 사항을 호출하여 배열로 저장한 후 각종 제어명령을 생성 · 실행한다. DATA FILE에서 호출한 내용 중 논리적 기능에 관한 내용으로 입 · 출력 관계식을 세우며, 입 · 출력 제어문자는 TRI-STATE BUFFER IC를 제어하여 신호흐름의 방향을 결정한다. (입 · 출력 핀 분리) 이 외에도 8BIT I/O INTERFACE 소자인 3개의 8255A IC에 대한 CONTROL WORD를 지정하고 각종 INDICATOR를 표시하여준다.

# 3. 실험결과 및 고찰

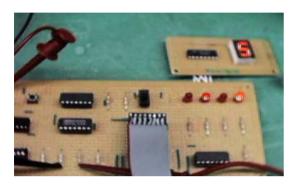

그림5와 같이 TEST Board를 구성하여 TEST시 양호한 출력 결과를 확인할 수 있었다. 이 TEST에 사용된 장비의 사양은 다음과 같다.

· TEST Board: 16진 up/down counter

Computer : 486DX2-50MHzOscilloscope : Tektronix 2440

· Target IC : 74LS86

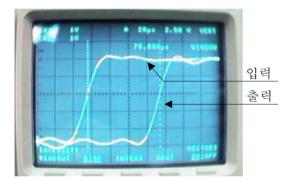

그림6은 74LS86의 가상 구현 후 두 입력단자 중한 입력단자를 Low로 하고 다른 한 입력단자에 구형파 입력을 가했을 때의 출력 파형을 보여준다. 이그림을 통하여 입력이 가해진 시간부터 출력이 나오기까지 약간의 지연시간이 발생함을 볼 수 있다. 이는 컴퓨터의 명령어 수행시간만큼의 지연시간이 생기는 것으로서 본 연구에서는 약 78.8 $\mu$ s 정도의 지연시간이 발생함을 볼 수 있다.

그림 5. TEST Board에서의 실행

그림 6. Delay time

# 4. 결 론

본 연구는 LOGIC IC나 임의의 DIGITAL 신호원을 PC상에서 프로그램으로 구현하여 출력해보고자하는 연구로서 입·출력 핀 선을 분리함으로서 서로의 간섭을 배재할 수 있으며 입력된 데이터의 비트연산을 통하여 원하는 출력신호를 생성할 수 있음을확인할 수 있었다.

# 참 고 문 헌

[1] N. Poojary, S. V. Krishnamurthy, and S. Dao. Medium Access Control in a Network of Ad Hoc Mobile Nodes with Heterogeneous Power Capabilities. In IEEE International Conference

- on Communications (ICC 2001), Vol. 3, pp. 872–877, 2001.

- [2] R. Ramanathan and R. Rosales-Hain. Topology Control of Multihop Wireless Networks using Transmit Power Adjustment. In INFOCOM 2000, Vol. 2, pp. 404-413, March 2000.

- [3] C. Lee, J. Jang, E.K. Park, S. Makkic. A simulation study of TCP performance over IEEE 1394 home networks. Computer Communications Vol. 26, pp. 670–678, 2003.

- [4] T. Tuan and K. Park. Multiple time scale congestion control for self-similar network traffic. *Performance Evaluation*, Vol. 36, pp. 358–386, 1999.

- [5] T. Tuan and K. Park. Multiple time scale redundancy for QoS-sensitive transport of real-time traffic. To appear in *Proc. IEEE INFOCOM '00,* 2000.

- [6] Peter Norten, "C++ Programming", 1993