# Plasma Oxidation Effect on Ultralow Temperature Polycrystalline Silicon TFT on Plastic Substrate

Yong-Hae Kim, Jaehyun Moon, Choong-Heui Chung, Sun Jin Yun, Dong-Jin Park, Jung Wook Lim, Yoon-Ho Song, and Jin Ho Lee IT Convergence & Comonents Lab., ETRI, Daejeon, Korea

Phone: +82-42-860-1751 , E-mail: yhakim@etri.re.kr

#### **Abstract**

The TFT performances were enhanced and stabilized by plasma oxidation of the polycrystalline Si surface prior to the plasma enhanced atomic layer deposition of  $Al_2O_3$  gate dielectric film. We attribute the improvement to the formation of a high quality oxide interface layer between the gate dielectric film and the poly-Si film. The interface oxide has a predominant effect on the TFT's characteristics, and is regulated by the gap distance between the electrode and the polycrystalline Si surface.

## 1. Introduction

Flexible displays are currently the subject of a great deal of interest due to their low weight, superior compactness, robustness and design flexibility compared with conventional glass-based displays. In order to realize a mechanically stable display, however, several issues must be resolved [1].

Inorganic materials have very different mechanical properties compared with plastic substrates; therefore, cracking and delamination may occur during the fabrication process and in operation. Furthermore, the thermal expansion coefficients of plastic substrates are much larger than those of inorganic materials and consequently, stresses during the deposition process are introduced. If a freestanding substrate is employed, the curvature of the inorganic film structures on plastic substrates changes during circuit fabrication, causing misalignment between the layers.

In order to prevent this misalignment, the plastic substrate is typically bonded to a rigid carrier. The adhesive used for bonding must withstand the TFT process temperatures and chemicals; therefore, the use of an adhesive necessitates a reduction of the maximum process temperature from the value that the substrate itself would normally withstand. The aforementioned issues as well as the low thermal resistance of most plastic substrates necessitate an ultra low temperature poly-Si (ULTPS) TFT process [2-6].

The crystallization of sputter deposited a-Si films was achieved by either excimer laser annealing [2-5] or sequential lateral solidification (SLS) [6,7]. Recently, we have reported on a successful SLS on a plastic substrate that yielded micron size large grain poly-Si films [8]. To prevent damage on the plastic substrates during the laser dopant activation, a quarter wavelength Bragg reflector, made by successive depositions of plasma-CVD silicon dioxide and silicon nitride film [5] and the oxide-silicon-oxide (SiO<sub>2</sub>-Si-SiO<sub>2</sub>) buffer structure [9], was suggested.

For gate dielectrics, the chemical vapor deposition SiO<sub>2</sub> [2,4-6], sputter deposition SiO<sub>2</sub> [4] and plasma enhanced atomic layer deposition (PEALD) Al<sub>2</sub>O<sub>3</sub> films [7,10-12] have been reported. A two-layer gate insulator composed of a thermal or plasma oxidized SiO<sub>2</sub> and PEALD Al<sub>2</sub>O<sub>3</sub> on silicon substrate [7,10] shows high quality characteristics. Because the plastic substrate on the thin carrier (silicon of 0.6 mm thick) was easily deformed during thermal processing, it is necessary to process the plastic substrate on a thicker carrier (glass of 1.1 mm thick).

The TFTs fabricated on the plastic substrate with a glass carrier [9] do not show the high quality characteristics which was observed on the silicon substrate [10] or on the stainless steel foil [11]. Aiming to improve and ultimately realize TFTs on plastic substrates, we focus on the interface between the poly-Si and  $Al_2O_3$  formed by the PEALD.

#### 2. Results

The buffer structure is designed to have an absorption layer sandwiched between the buffer oxide films [9]. Because a-Si film as an absorption layer effectively absorbs the laser light during the dopant activation process using a laser, the plastic substrate is protected.

After laminating the plastic substrate on a glass wafer, we sputtered a buffer oxide I layer of 250 nm thick  $\mathrm{SiO}_2$  film on the plastic substrate using RF-magnetron sputter deposition method at 300 W and 0.15 Pa.

Subsequently, we deposited an 80 nm thick a-Si film for an absorption layer at RF power of 1 kW and Ar pressure of 0.48 Pa. Then, a buffer oxide II of  $\text{SiO}_2$  film was deposited on the absorption layer using RF-magnetron sputter deposition method at 300 W and 0.15 Pa.

Due to the thermal restrictions, ULTPS-TFT processes have met difficulties in annealing the interface between channel and the gate dielectrics. We tried to oxidize the Si surface with pulsed O<sub>2</sub> plasma at a condition of 300 W for 30 min before the Al<sub>2</sub>O<sub>3</sub> deposition by PEALD.

Prior to the oxidation, the surface of the Si substrates was cleaned with a 100:1 hydrofluoric acid solution to remove the native oxide layer.

We have varied the gap distance between the electrode and the sample surface to observe the effect on the TFT performance. Usually, to facilitate the transport of reaction gas species, PEALD uses a narrow gap distance [14]. The Si surface was cleaned to remove the native oxide layer. The working conditions were set to produce 50 nm thick Al<sub>2</sub>O<sub>3</sub> layers with prior plasma oxidation at 180 °C.

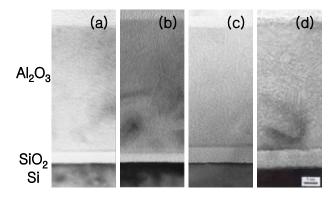

Figure 1 shows transmission electron microscopy (TEM) images of SiO<sub>x</sub>/Al<sub>2</sub>O<sub>3</sub> interfaces with gap distance variation. The interface gains thickness upon increasing gap distance.

Figure 1. Transmission electron microscopy images of interface layer,  $SiO_x$ , and  $Al_2O_3$  layer with a gap distance variation both in the plasma oxidation and in the 50 nm  $Al_2O_3$  deposition. (a) 3.0 mm, (b) 3.6 mm, (c) 4.2 mm, and (d) 4.8 mm.

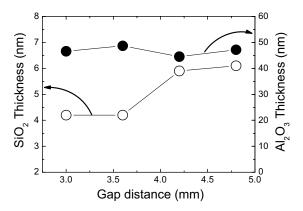

Figure 2. Thickness variation of SiO<sub>x</sub> and Al<sub>2</sub>O<sub>3</sub> layer with the gap distance obtained from TEM observation.

The result of fig. 1 was quantitatively analyzed in fig. 2. As can be seen, the  $SiO_x$  layer thickness is rather insensitive up to gap distance of 3.6 mm, and then increases significantly up to 4.2 mm. The  $Al_2O_3$  layer thickness do not vary with the gap distance.

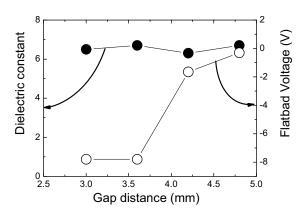

Figure 3. Changes in the dielectric constants and flatband voltages of 50 nm grown gate dielectric with a gap distance variation using C-V measurement.

Figure 3 shows the changes in the dielectric constants and flatband voltages of 50 nm thick gate dielectric with a gap distance variation using C-V measurement. Apparently, the dielectric constants show no explicit dependency on the gap distance. However, the

flatband voltages approach zero voltage as the gap distance is increased.

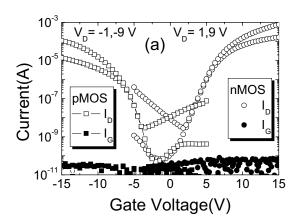

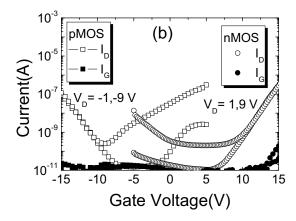

Figure 4 shows the transfer characteristics of the nMOS and pMOS TFTs fabricated at 180 °C on plastic substrates. Al<sub>2</sub>O<sub>3</sub> gate dielectric was grown (a) at a 4.0 mm and (b) at a 3.3 mm gap distance. The high performances of the nMOS/pMOS TFTs with mobilities of 154 and 33 cm2/Vs, threshold voltages of 5.8 and -7.3 V and sub-threshold swings of 1.0 and 0.78 V/dec, respectively, were obtained at a 4.0 mm gap distance while poor performances were obtained at a 3.3 mm gap distance.

Figure 4. Transfer characteristics of the nMOS/pMOS TFT fabricated at 180 °C at (a) 4.0 mm and (b) 3.3 mm gap distance.

## 3. Conclusion

The TFT performance was enhanced with increasing the gap distance in the PEALD process for dielectric deposition. We attribute this to the formation of a high quality oxide interface layer between the gate dielectric film and the poly-Si film.

### 4. Acknowledgements

The authors would like to thank the Korea Ministry of Information and Communication for financial support.

#### 5. References

- [1] S. Wagner, H. Gleskova, I-C. Cheng, J. C. Sturm, and Z. Suo, "Mechanics of TFT Technology on Flexible Substrates," in *Flexible Flat Panel Displays*, G.. P. Crawford, Ed. West Sussex, England: John Wiley & Sons Ltd., 2005, pp. 263-282.

- [2] D. P. Gosain, T. Noguchi, and S. Usui, *Jpn. J. Appl. Phys. Part* 2, vol. 39, pp. L179-L181, Mar. 2000.

- [3] T. Serikawa and F. Omata, *Jpn. J. Appl. Phys. Part* 2,vol. 39, pp. L393-L395, May 2000.

- [4] P. G. Carey, P. M. Smith, S. D. Theiss, and P. Wichboldt, *J. Vac. Sci. Technol.*, vol. A17, pp. 1946-1949, Jul./Aug. 1999.

- [5] F. Lemmi, W. Chung, S. Lin, P. M. Smith, T. Sasagawa, B. C. Drews, A. Hua, J. R. Stern, and J. Y. Chen, *IEEE Electron Device Lett.*, vol.25, pp. 486-488, 2004.

- [6] J. Y. Kwon, D. Y. Kim, H. S. Cho, K. B. Park, J. S. Jung, J. M. Kim, Y. S. Park, and T. Noguchi, *IEICE Trans. Electron.*, vol. E88-C, pp. 667-671, 2005.

- [7] Y. H. Kim, C. Y. Sohn, J. W. Lim, S. J. Yun, C. S. Hwang, C. H. Chung, Y. W. Ko, and J. H. Lee, *IEEE Electron Device Lett.*, vol. 25, pp. 550-552, 2004.

- [8] Y. H. Kim, C. H. Chung, S. J. Yun, J. Moon, D. J. Park, D. W. Kim, J. W. Lim, Y. H. Song, and J. H. Lee, *Thin Solid Films*, vol. 493, pp. 192-196, 2005.

- [9] Y. H. Kim, C. H. Chung, J. Moon, G. H. Kim, D. J. Park, D. W. Kim, J. W. Lim, S. J. Yun, Y. H. Song, and J. H. Lee, *IEEE Electron Device Lett.*, accepted.

- [10] J. W. Lim, S. J. Yun, Y. H. Kim, C. Y. Sohn, and J. H. Lee, *Electrochem. Solid-State Lett.*, vol. 7, pp. G185-G187, 2004.

- [11] Y. Moon, D. J. Park, C. H. Chung, Y. H. Kim, M. H. Lee, D. W. Kim, J. W. Lim, S. J. Yun, and J. H. Lee, *IEEE Electron Device Lett.*, submitted.

- [12] J. W. Lim and S. J. Yun, *Electrochem. Solid-State Lett.*, vol. 7, pp. F45-F48, 2004.

- [13] S. C. Ha, E. Choi, S. H. Kim, and J. S. Roh, *Thin Solid Films*, vol. 476, pp. 252-257, 2005.

[14] M. Goto, K. Azuma, T. Okamoto, and Y. 7038, 2003. Nakata, *Jpn. J. Appl. Phys.*, vol. 42, pp. 7033-