# Threshold Voltage Control of Pentacene Thin-Film Transistor with Dual-Gate Structure

Jae Bon Koo\*, Chan Hoe Ku, Sang Chul Lim, Jung Hun Lee, Seong Hyun Kim, Jung Wook Lim, Sun Jin Yun, Yong Suk Yang, and Kyung Soo Suh Electronics and Telecommunications Research Institute, Yuseong-gu, Daejeon 305-700, Korea

Phone: 82-42-860-5470, E-mail: kjb0706@etri.re.kr

## Abstract

We have presented a comprehensive study on threshold voltage  $(V_{th})$  control of organic thin-film transistors (OTFTs) with dual-gate structure. The fabrication of dual-gate pentacene OTFTs using plasma-enhanced atomic laver deposited (PEALD) 150 nm thick Al<sub>2</sub>O<sub>3</sub> as a bottom gate dielectric and 300 nm thick parylene or PEALD 200 nm thick Al<sub>2</sub>O<sub>3</sub> as both a top gate dielectric and a passivation layer is reported. The  $V_{th}$  of OTFT with 300 nm thick parylene as a top gate dielectric is changed from 4.7 V to 1.3 V and that with PEALD 200 nm thick Al<sub>2</sub>O<sub>3</sub> as a top gate dielectric is changed from 1.95 V to -9.8 V when the voltage bias of top gate electrode is changed from -10 V to 10 V. The change of V<sub>th</sub> of OTFT with dual-gate structure has been successfully understood by an analysis of electrostatic potential.

#### 1. Introduction

Organic electronics have recently become a promising technology for applications requiring low-cost, large area coverage, mechanical flexibility, and low temperature processing. Organic thin film transistors (OTFTs) have been proposed for various applications of electronic circuits, including radio-frequency identification (RFID) tag, digital paper displays, back planes for flexible active-matrix liquid crystal displays (AMLCDs) and organic light-emitting diodes (AMOLEDs)[1,2]. The device performances of OTFTs have improved dramatically over the past decade. The carrier mobilities of OTFTs are similar to or even higher than those typically obtained with hydrogenated amorphous silicon TFTs, which have found widespread use in AMLCDs [1]. In particular, the OTFTs based on pentacene have received considerable attention in recent years due to their superior performances such as high field-effect mobility and large on/off current ratio [1]. The remaining issues on the development and the mass-production of practical OTFTs are the improvement of passivation performance and the control of electrical parameters such as threshold voltage (V<sub>th</sub>) and oncurrent. These problems can be simultaneously solved using dual-gate (DG) OTFT. Furthermore, the dual-gate geometry adapts to different bias configurations and offers higher flexibility of operation with respect to single-gate devices. Recently, the results on the control of V<sub>th</sub> of pentacene and polymer OTFT with DG structure were reported [3-5]. In this work, the control of electrical parameters and the long-term stability of DG OTFTs have been investigated and discussed.

## 2. Experimental Details

Si wafers with thermally grown 300 nm SiO<sub>2</sub> were used as substrates for these experiments. A 50 nm Ti was deposited by e-beam evaporator through a shadow mask for the patterned bottom gate electrode (G1). A PEALD 150 nm thick Al<sub>2</sub>O<sub>3</sub> film was deposited at 150 °C to form bottom gate dielectric using trimethylaluminum (TMA) precursors and O<sub>2</sub> gas mixed with N<sub>2</sub> gas. The breakdown field of 9 MV/ cm and the capacitance (C<sub>ox</sub>) of 41 nF/cm<sup>2</sup> were obtained in our PEALD Al<sub>2</sub>O<sub>3</sub> [6]. Source (S) and drain (D) consisting of 3 nm thick Ti and 80 nm thick Au layers was deposited on top of Al<sub>2</sub>O<sub>3</sub>. The bottom gate dielectric surface was treated hexamethyldisilane (HMDS) as the selforganizing materials, which had been used to improve the quality of the organic/dielectric interface [7], followed by the deposition of a 100 nm thick pentacene layer. The substrate with

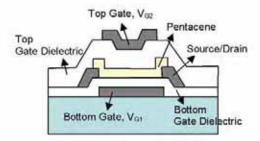

bottom gate OTFT was then coated with a 300 nm thick parylene layer (Cpar=7.15 nF/cm<sup>2</sup>) or a 200 nm thick PEALD Al2O3 layer deposited at 100 °C (CAI203=26.9 nF/cm<sup>2</sup>). Parylene is a material commonly used as a passivation layer on top of pentacene layer [8] and the PEALD Al2O3 deposited at 100 °C is a recently developed new passivation material without damage on pentacene layer [9]. Finally, a 50 nm thick Ti layer was deposited to form the top gate electrode (G2). structure cross-sectional bias configuration of OTFT are schematically shown in Fig. 1. We evaluated the transfer characteristics of OTFTs using Keithley 4200 semiconductor parameter analyzer in the dark at room temperature.

Fig. 1. Schematic structure and bias configuration of the bottom contact DG OTFT device.

# 3. Results and Discussion

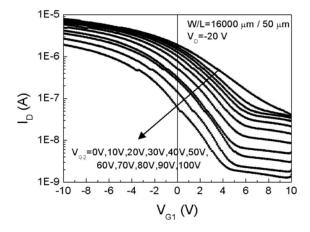

The drain current (ID)-gate voltage (VG) curves in Fig. 2 show the transfer characteristics of the DG OTFT with PEALD 150 nm Al<sub>2</sub>O<sub>3</sub> as a bottom gate dielectric and with 300 nm parvlene as a top gate dielectric. The bottom OTFT of this DG structure had a saturation mobility of 0.01 cm<sup>2</sup>/Vs, V<sub>th</sub> of 4.7 V, subthreshold swing (SS) of 1.12 V/decade, and on/off current ratio of 6.3×10<sup>5</sup>. Mobility and Vth were obtained from the linear fit of the plot, ID 1/2 vs. Vg. In case of the OTFT with a top contact S/D structure using PEALD Al2O3. we obtained a saturation mobility of 0.1-0.5 cm2/Vs. Even though the properties of top contact device was much better than those of bottom contact device, especially with respect to mobility, we adopted the bottom contact configuration for considering the development and mass production of practical OTFTs and integration of inverter.

When V<sub>G2</sub> was 0 V, the transfer curves of first and second scan were exactly identical. Based on this successive scan, we concluded that there is no bias stress effect in our devices which consists of a progressive shift of the Vth towards negative voltage as the gate electrode is biased and the stability of our device is enough for testing the control of V<sub>th</sub> using the top gate bias. When V<sub>G2</sub>, top gate bias was varied from -10 V to 10 V in steps of 5 V, the Vth of bottom OTFT was systematically shifted from 4.7 V to 1.3 V as shown in Fig. 2(a). The top OTFT of the DG structure had a saturation mobility of 0,005 cm<sup>2</sup>/Vs, Vth of -4.8 V, SS of 4.26 V/decade, and on/off current ratio of 1.2×105. When V<sub>GI</sub>, bottom gate bias was varied from -10 V to 10 V in steps of 5 V, the Vth of top OTFT was intensely shifted from 15.2 V to -20 V as shown in Fig. 2(b).

Fig. 2. (a) The change of transfer characteristics of the bottom OTFT of DG structure with the change of top gate bias,  $V_{\rm G2}$  and (b) that of the top OTFT with the change of bottom gate bias,  $V_{\rm G1}$ .

The shift of transfer curve can be explained by the body effect in a Si transistor [10]. In a bulk device, the body effect is defined as the dependence of the  $V_{th}$  of the bottom gate OTFT on the top gate bias. The  $V_{th}$  as a function of top gate bias can be predicted from Eq. 1

$$\frac{dV_{th}}{dV_{G2}} = -\frac{C_{pen}C_{top}}{C_{bottom}(C_{pen} + C_{top})} \cong -\frac{C_{top}}{C_{bottom}}$$

(1)

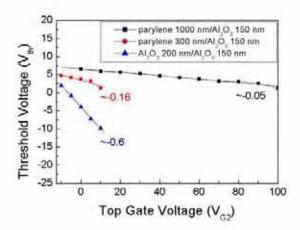

where C<sub>bottom</sub>, C<sub>pen</sub>, and C<sub>top</sub> are the capacitance of bottom gate dielectric, pentacene semiconductor, and top gate dielectric, respectively [11]. Fig. 3 shows the transfer characteristics of DG OTFT with PEALD 150 nm Al<sub>2</sub>O<sub>3</sub> as a bottom gate dielectric and with 1000 nm parylene as a top gate dielectric. When V<sub>G2</sub>, top gate bias was varied from 0 V to 100 V in steps of 10 V, the Vth was only shifted from 6.6 V to 1.3 V. In the case of low C<sub>top</sub>/C<sub>bottom</sub>, the large top gate voltage was needed to shift V<sub>th</sub> value as shown in Fig. 3. From the DG OTFT with 300 nm thick parylene, as shown in Fig. 2(a), the measured slope of  $dV_{\text{th}}\!/dV_{\text{G2}}$  was -0.16 and that from the DG OTFT with 1000 nm thick parylene was -0.05, which were in agreement with C<sub>top</sub>/C<sub>bottom</sub> of -0.17 and -0.052, respectively. In the case of DG OTFT with PEALD 200 nm Al<sub>2</sub>O<sub>3</sub> deposited at 100 °C as a top gate dielectric, the measured dV<sub>th</sub>/dV<sub>G2</sub> was -0.6, which was also in agreement with C<sub>top</sub>/C<sub>bottom</sub> of -0.66.

Fig. 3. The change of transfer characteristics of OTFT with PEALD 150 nm Al<sub>2</sub>O<sub>3</sub> as a bottom

gate dielectric and with 1000 nm parylene as a top gate dielectric when  $V_{\rm G2}$  was varied from 0 V to 100 V in steps of 10 V.

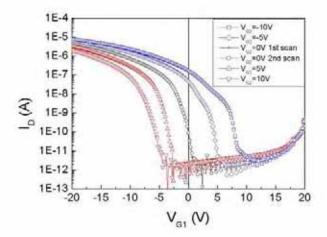

The relationship between V<sub>G2</sub> and V<sub>th</sub> of DG OTFT with different combinations of bottom and top gate dielectrics was shown in Fig. 4. In silicon metal-oxide-semiconductor field effect transistors (MOSFETs), which are widely used as electronic devices, V<sub>th</sub> can be controlled by changing the doping level of semiconductor. However, in case of OTFT, V<sub>th</sub> control by doping is not available yet. The DG OTFT used in this work gives an alternative for artificially controlling V<sub>th</sub> and oncurrent. Furthermore, the top gate dielectric layer can play an additional role of passivation for OTFT devices. As mentioned above, parylene is a commonly used passivation material and the PEALD Al<sub>2</sub>O<sub>3</sub> deposited at a low temperature is a newly developed passivation layer by the authors. Fig.5 shows the transfer characteristics of DG OTFT with PEALD 150 nm Al<sub>2</sub>O<sub>3</sub> deposited at 100 °C as a top gate dielectric after the shelf storage of 6 months at room temperature in air. The initial  $V_{th}$  of this device was about -3.9 V and that after the shelf storage it was slightly positive shifted to -3.5 V. Other electrical parameters such as mobility, off current, and subthreshold slope were almost identical, compared with the initial values. The relationship between V<sub>G2</sub> and V<sub>th</sub> was still clearly observed meaning the pentacene OTFT was not seriously degraded even after 6 months storage as shown in Fig. 5. We also checked the passivation performances of DG OTFT with parylene as a top gate dielectric after the storage of 6 months. Some degradation of pentacene active layer happened and that caused the decrease of mobility and on-current and the increase of subthreshold slope and off-current. It is believed that the passivation performance of PEALD Al<sub>2</sub>O<sub>3</sub> is superior to that of parylene.

Although  $V_{th}$  of OTFT can be controlled by modifying the surface of gate dielectric layer with self-assemble monolayer (SAM) [12,13], such approaches are still far from practical use due to the reliability of manufacturing process and the instability in moisture on SAM coating. The present work shows that DG OTFT can be an applicable and useful method for the fabrication of practical OTFTs.

#### 4. Conclusion

We reported on the fabrication of DG pentacene OTFT using parylene and PEALD Al<sub>2</sub>O<sub>3</sub> as top gate dielectrics. The V<sub>th</sub> shift of DG OTFT was clucidated by an analysis of the electrostatic potential. The control of electrical parameters of OTFT such as V<sub>th</sub> and on-current and the improvement of passivation performance could be simultaneously solved using a DG OTFT. The present work suggests that the PEALD Al<sub>2</sub>O<sub>3</sub>, which is possible of low temperature deposition onto plastic substrate, is a good candidate for both gate dielectric and passivation layer of DG OTFT.

Fig. 4. The dependence of V<sub>th</sub> on V<sub>G2</sub> for DG OTFTs with different combinations of bottom and top gate dielectric.

Fig. 5. The change of transfer characteristics of the DG OTFT with 150 nm thick PEALD Al<sub>2</sub>O<sub>3</sub> as a bottom gate dielectric and with 200 nm thick PEALD Al<sub>2</sub>O<sub>3</sub> as a top gate dielectric when V<sub>G2</sub> was varied from -10 V to 10 V in steps of 5 V. The DG OTFT was measured after the shelf storage of 6 months at room temperature in air.

# 5. Acknowledgements

This work has been supported financially by the Korean Ministry of Science and Technology through the NRL program.

## 6. References

- C.D. Dimitrakopoulos and P.R.L. Malenfant, Adv. Mater. 14, 99 (2002).

- [2] G. Horowitz, Adv. Mater. 10, 365 (1998).

- [3] S. Iba, T. Sekitani, Y. Kato, T. Someya, H. Kawaguchi, M. Takamiya, T. Sakurai, and S. Takagi, Appl. Phys. Lett. 87, 23509 (2005).

- [4] M. Morana, G. Brest, and C. Brabec, Appl. Phys. Lett. 87, 153511 (2005).

- [5] G.H. Gelink, E.van Veenendaal, and R. Cochoorn, Appl. Phys. Lett. 87, 73508 (2005).

- [6] J.W. Lim and S.J. Yun, Electrochem. Solid-State Lett. 7, F45 (2004).

- [7] I. Yagi, K. Tsukagoshi, and Y. Aoyagi, Appl. Phys. Lett. 86, 103502 (2005).

- [8] T. Sekitani, S. Iba, Y. Kato, Y. Noguchi, T. Someya, and T. Sakurai, Appl. Phys. Lett. 87, 73505 (2005).

- [9] J.H. Lee, S.H. Kim, J.B. Koo, C.H. Ku, S.C. Lim, J.W. Lim, S.J. Yun, J. Jang, and T. Zyung, accepted to J. Kor. Phys. Soc. (2006).

- [10] S. Dimitrijev, "Understanding Semiconductor Devices", Oxford University Press, New York, USA, 2000.

- [11] T. Ernst, S. Cristoloveanu, G. Ghibaudo, T. Ouisse, S. Horiguchi, Y. Ono, Y. Takahashi, and K. Murase, *IEEE Trans. Electron Devices* 50, 830 (2003).

- [12] S. Kobayashi, T. Nishikawa, T. Takenobu, S. Mori, T. Mitani, H. Shimotani, N. Yoshimoto, S. Ogawa, and Y. Iwasa, *Nat. Meater.* 3, 317 (2004).

- [13] K.P. Pernstich, S. Haas, D. Oberhoff, C. Goldmann, D.J. Gundlach, B. Batlogg, A.N. Rashid, and G. Schitter, J. Appl. Phys. 96, 6431 (2004).