## Thin Film Transistor (TFT) Pixel Design for AMOLED

# Min-Koo Han, Jae-Hoon Lee, Woo-Jin Nam School of Electrical Engineering, Seoul National University, Seoul, Korea Phone: +82-2-880-7248, Fax: +82-2-871-7992, E-mail: mkh@snu.ac.kr

### **Abstract**

Highly stable thin-film transistor (TFT) pixel employing both low temperature polycrystalline silicon (LTPS) and amorphous silicon (a-Si) for active matrix organic light emitting diode (AMOLED) is discussed. ELA (excimer laser annealing) LTPS-TFT pixel should compensate  $I_{OLED}$  variation caused by the non-uniformity of LTPS-TFT due to the fluctuation of excimer laser energy and amorphous silicon TFT pixel is desired to suppress the decrease of  $I_{OLED}$  induced by the degradation of a-Si TFT. We discuss various compensation schemes of both LTPS and a-Si TFT employing the voltage and the current programming.

### 1. Introduction

Recently, active matrix organic light emitting diode (AMOLED) display has attracted a considerable attention due to a brightness, wide viewing angle, and compactness [1]. AMOLED employing both LTPS and a-Si TFT backplane can make a high resolution and large-size display because TFT device can supply a small OLED current ( $<2\mu A$ ).

Low temperature polycrystalline silicon thin film transistors (LTPS-TFTs) should supply an accurate and stable current in each pixel for AMOLED driving. However, the electrical properties of LTPS-TFT, such as the threshold voltage and field effect mobility, suffer from the non-uniformity in device to device [1]. The non-uniform characteristics of LTPS-TFT originate from the inherent process variation of the crystal growth in polycrystalline film. The LTPS-TFT pixel circuit should compensate the non-uniform characteristics of poly-Si TFT for the uniform luminance in the display panel. The conventional AMOLED pixel and the previous reported pixels which use compensation scheme are reviewed [1-5].

Hydrogenated amorphous silicon (a-Si:H) TFT has also attracted a considerable attention as a pixel element for AMOLED backplane because the uniformity and fabrication process are well established [6-10]. It is well known that a-Si:H TFT has suffered from  $V_{th}$  degradation due to a charge trapping and defect state creation induced by an electrical bias stress. The decrease of output current in a-Si:H TFT due to  $V_{th}$  degradation causes a decrease of brightness in AMOLED display.

The purpose of this paper is to discuss various compensation schemes of both LTPS and a-Si TFT employing the voltage and the current programming for a high quality AMOLED display.

### 2. Discussion

## 2.1. LTPS-TFT pixel design for AMOLED

In the AMOLED pixel design, OLEDs (Organic light emitting diodes) are presently fabricated with the anode (hole injection electrode) and the cathode (electron injection electrode). The current driving transistor is conventionally connected from the supply voltage to the anode of OLED. Therefore, p-type devices are desired to prevent variations in the OLED material turn on voltage from leading to current variations in the OLED material.

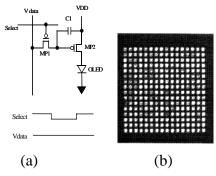

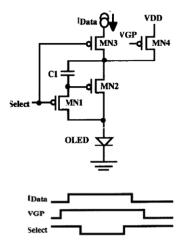

The simplest AMOLED pixel which has pixel memory uses two transistors and one capacitor. One TFT drives the current for the OLED and another TFT acts as a switch to sample and hold a voltage onto the storage capacitor C1 as shown Fig. 1 (a). It is noted that variations in the threshold voltage, carrier mobility, or series resistance will directly impact the uniformity of the saturation current of OLED driving TFT and consequently the brightness of the display. The major factor of non-uniformity current is the threshold voltage variation of the OLED drive transistors. The current flow through the LTPS TFT suffers from large pixel to pixel variations due to the nature of the LTPS grain growth. The effects of TFT non-uniformity on the conventional 2 transistor pixel design of Fig. 1 (a) were reported as shown in Fig. 1 (b). The local brightness non-uniformity was almost 17%. The OLED current driven by the TFT is expressed by the equation (1).

$$\begin{split} &I_{OLED} = 1/2 \cdot k \cdot (V_{GS} - V_{TH})^2 \\ &= 1/2 \cdot k \cdot (V_{DATA} - V_{DD} - V_{TH})^2 \quad ..... \quad (1) \\ &(\text{here, k is } \mu_{eff} \cdot C_{OX} \cdot W/L \text{ and } V_{TH} < 0) \end{split}$$

Fig. 1 (a) Conventional AMOLED pixel circuit employing two transistors and one capacitor. (b) the brightness non-uniformity (17%) of the conventional 2-TFT pixel [1].

## 2.1.1. Voltage programmed LTPS-TFT pixel

In order to compensate the OLED current variation in LTPS-TFT AMOLED display, several voltage programming and current programming methods have been already reported [1-5]. The voltage programming method addresses the data voltages to the pixel circuit, while the current programming method addresses the current data to the pixel.

However, it is noted that both the methods use voltages as data which are modulated and stored finally at the gate node of the OLED driving TFT.

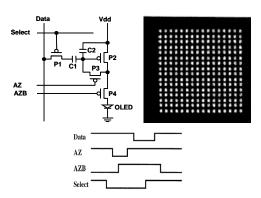

In the reported voltage modulation driving method, R.M.A Dawson's group reported an effective method to compensate for the threshold voltage variation of LTPS TFTs [1]. The AMOLED pixel is shown in Fig. 2 where two additional transistors are used to auto zero the threshold voltage of the current drive transistor. The timing diagram is shown in Fig. 2. The improvement of the pixel to pixel brightness uniformity obtained using this technique is demonstrated in Fig. 2. This pixel does not rely on the settling time of the OLED to calibrate out the TFT threshold voltage variations. It is programmed by applying a voltage to the gate of driving TFT which supplies a constant current throughout the frame time, so it does not rely on the charging time of the OLED for programming.

The demerits are the additional signal lines (AZ/AZB) to control the  $V_{TH}$  cancelling operation. The signal lines cover all the row arrays for the scanning the pixels as the scan signal so that the layout area consumption is increased and the pixel aperture ratio is considerably reduced.

Fig. 2. V<sub>th</sub> compensated pixel (4 TFTs, 2 capacitors and 2 additional signals). The improvement of the pixel to pixel brightness uniformity [1].

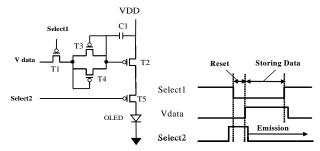

Fig. 3 shows a simple voltage programming  $V_{th}$  compensated pixel, which reduces an additional signal lines [2]. It can compensate  $V_{th}$  variation of LTPS-TFT and kink effect inevitable of LTPS-TFT because it has a cascode configuration.

Fig. 3. The reported AMOLED pixel circuit employing a voltage modulation which compensates the threshold voltage variation of poly-Si TFT, and its timing diagram [2].

Although the voltage programmed (or modulated) pixel circuits have provided an evident performance of non-uniformity compensation, they still suffer from the  $I_{OLED}$  non-uniformity due to the other variation factors. One is the mobility variation and it cannot be memorized itself. It is rather difficult to compensate the mobility variation of LTPS TFTs in the voltage modulation method. On the other hand, it is almost

possible to compensate the non-uniform mobility of TFT as well as the threshold voltage of TFT in the current programming method.

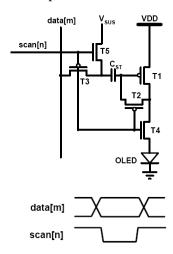

The supply voltage drop phenomena is also the serious problem in the voltage programmed pixel circuits [3]. The OLED current flows in each pixel are supplied by the voltage source (typically  $V_{\rm DD}$ ). Although the voltage supply line has a low resistance across the panel, it undergoes the voltage drop by the large amount of current flows ( $\sim$  mA) required in a column array. Fig. 4 has been reported by Choi et al. to compensate the supply voltage drop problem in the voltage programmed pixel circuit [3]. It employs additional supply voltage ( $V_{\rm SUS}$ ) for a reference voltage and n-type TFT for switching. When the n-type TFT is replaced by p-type, an additional signal line will be added, apart from the select line.

Fig. 4. The reported AMOLED pixel circuit employing a reference voltage source  $V_{SUS}$  which compensates the  $V_{DD}$  supply voltage drop as well as the threshold voltage variation of poly-Si TFT [3].

## 2.2. Current-programmed LTPS-TFT pixel

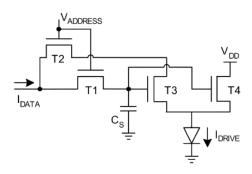

The current programming method employs the current source unit from the data driver and addresses the current data to the pixel circuit in which the data current is memorized during the emission frame. It should be noted that the scheme can compensate both threshold voltage and mobility variations of poly-Si TFTs. They are free from cross talk caused by the voltage drop in power supply line, while most of voltage modulation schemes suffer from it especially when we go to larger panels or higher brightness [1]. In the pixel circuit, the data current ( $I_{DATA}$ ) determines

a drive voltage ( $V_{\text{GATE}}$ ) of the driving TFT to flow the OLED current with respect to  $I_{\text{DATA}}$ .

The current programming pixel was also reported by Dawson et al., and is shown in Fig. 5 with timing diagram. Programming of this pixel is accomplished by turning off MN4 with VGP. And MN1 and MN3 are turned on by SELECT, which drives the data current (I<sub>DATA</sub>). This adjusts and sets the gate to source voltage of MN2 which is stored on C1. Once the programmed voltage (V<sub>GATE</sub>) is stored, the pixel can be connected to the power supply for illumination. However, the large load capacitance of column array should be charged to  $V_{\text{GATE}}$  by  $I_{\text{DATA}}$ . Therefore, very small current of IDATA at low brightness may lead to long programming time. The settling time of the OLED is an issue for this pixel, and it is applicable to low resolution displays which have longer row times.

Fig. 5. The reported current programming AMOLED pixel in which I<sub>DATA</sub> is memorized and V<sub>GATE</sub> of MN2 is determined to allow I<sub>DATA</sub>. Current programming schemes have to manage very small current at low brightness, it may lead to unrealistically long programming time [1].

The data current scaling scheme which employs a current-mirror structure has been reported. The widely used assumption that the neighboring TFTs in each pixel have an identical electrical characteristics, such as threshold voltage and mobility is employed in the current scaling pixel.

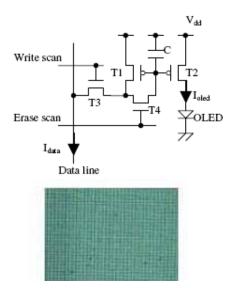

The other type of current programming method was reported by Sasaoka et. al [4]. Fig. 6 is the developed pixel circuit and the photograph, which shows an improvement of the luminance uniformity.

Fig.6. The reported current programming AMOLED pixel employing a parallel current-mirror structure and a luminance uniformity [4].

When the data current is applied to the Data line, the current I<sub>OLED</sub> through T2 will be scaled down by a current mirror T1. For the current mirror configuration, it should be assumed that the neighboring **TFTs** have identical electrical characteristics, which is also often used in voltage programming method. By defining the channel width of T1 larger than that of T2, the data current becomes larger than OLED current, which made write operation fast enough even at low brightness compared with the previous current programming method.

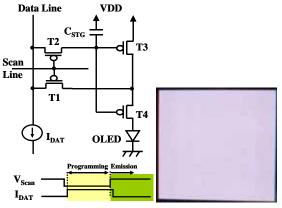

Fig.7. The reported current programming AMOLED pixel using a serial current-mirror structure [5],

The current scaling scheme has been also reported and the scaling down capability is increased [5]. It employs the p-type poly-Si TFTs only without additional signal line as shown in Fig. 7. The data current is memorized by T3 in the programming period and the  $V_{GATE}$  of T3 is stored in  $C_{STG}$ . In the emission period, the T4 is turned on and the memorized current would be decreased and scaled down by the size effect of T3 and T4. The photograph of luminance at 50 nit. The non-uniformity of luminance is less than 10%.

Although the current programmed pixel can supply a better compensation capability compared with a voltage programmed pixel, the accurate IC and the current data driver, which can reduce a pixel charging time, should be developed for a mass production.

## 2.3. a-Si TFT pixel design for AMOLED

Hydrogenated amorphous silicon (a-Si:H) TFT has gained considerable attention as a pixel element for AMOLED backplane [6-10]. When a gate and drain bias is applied to a-Si TFT pixel, a drain current of a-Si TFT is decreased because a threshold voltage (V<sub>th</sub>) of a-Si TFT is increased due to the charge trapping into SiN<sub>x</sub> gate-insulator and a defect state creation in a-Si channel layer [11]. It is well known that the decrease of output current in a-Si TFT due to an increased V<sub>th</sub> causes a decrease of brightness in the AMOLED display[8]. Several pixel circuits employing V<sub>th</sub> compensated scheme have been reported to compensate the decrease of OLED current (I<sub>OLED</sub>) by increasing a gate voltage of a-Si TFT [6-10].

Fig. 8 shows a voltage programmed a-Si TFT pixel circuit developed by Goh et.al [6].

Fig. 8. The voltage programmed  $V_{th}$  compensated a-Si TFT pixel circuit [6].

The data voltage is written to the source node of DTFT (current driving TFT) so that  $V_{\text{data}} + V_{\text{th}}$  of DTFT is memorized by discharging the gate node of DTFT. When  $V_{\text{th}}$  of OLED is degraded, the OLED current of this pixel may be decreased.

Fig. 9. The voltage programmed  $V_{th}$  compensated a-Si TFT pixel considering  $V_{th}$  shift of OLED [7].

Fig. 9 shows the voltage programmed  $V_{th}$  compensated a-Si TFT pixel considering  $V_{th}$  shift of OLED developed by Jung [7]. The pixel in Fig. 9 employs a bootstrapping in order to obtain  $I_{OLED}$  insensitive to OLED  $V_{th}$  shift. Although  $V_{th}$  of a-Si TFT as well as OLED would be compensated in each pixel, the degradation of SW3 may force D-TFT into the linear region so that a slight decrease of  $I_{OLED}$  may be occurred.

Fig. 10. The current programmed a-Si TFT pixel employing a current-mirror structure [8].

Fig. 10 is a representative current programmed pixel reported by Nathan [8]. When the data current is applied to the data line, the current  $I_{OLED}$  through T4 will be scaled down by a current mirror T3. For the

current mirror configuration, it should be assumed that the neighboring TFTs have identical electrical characteristics.

When only  $V_{th}$  storing scheme is used in the a-Si:H TFT pixel circuit, the gate voltage is increased to overcome the increased  $V_{th}$ . Increased gate voltage in  $V_{th}$  stored pixel causes a larger  $V_{th}$  shift compared with conventional 2-TFT pixel so that it can fail when the gate voltage comes to the supply voltage. Therefore, a driving scheme using a negative bias to reduce degradation of a-Si:H TFT itself is recently reported [9-10].

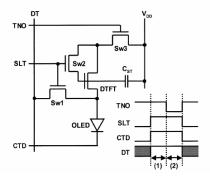

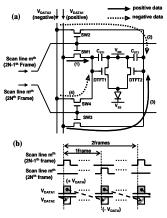

Fig. 11 shows that the a-Si:H TFT pixel circuit employing a negative bias annealing to improve a stability of a-Si TFT [9]. The pixel circuit consists of two driving transistors (DTFT1 and DTFT2) with storage capacitors (C<sub>ST1</sub> and C<sub>ST2</sub>). And switching transistors SW1 and SW3 provide positive data. The switching transistors SW2 and SW4 are employed to recover the degradation of a-Si:H TFT by negative bias. The scan signal for selecting horizontal line is alternately supplied through two scan lines every frame. In the odd frame, when the scan  $m^{th}$  ((2N-1)<sup>th</sup> frame) line is supplied with high scan signal, switching TFTs SW1 and SW2 are turned on. As SW1 is turned on, storage capacitor C<sub>ST1</sub> connected to the drain and gate of the driving TFT DTFT1 is charged and this maintains positive data "+V<sub>DATA</sub>" throughout one frame time, as it is indicated by the solid line (1) in Fig. 11(a). Simultaneously, SW2 is turned on, and the storage capacitor CST2 in the opposite side stores negative data "-VDATA" of the previous frame induced through V<sub>DATA2</sub> line, as indicated by a dotted line (2) in Fig. 11(a). Subsequently, when the scan signal is low, the charged  $C_{ST1}$  and  $C_{ST2}$  will supply "+V  $_{DATA}$  " and "-V<sub>DATA</sub>" to DTFT1 and DTFT2, respectively.

Then DTFT1 results in the emission of OLED, and DTFT2 is annealed by the negative biasing during the frame time. In the next frame  $2N^{th}$  (meaning the even frame), this circuit may repeat odd frame operation, however, with reversed polarity of the charged voltage in storage capacitors  $C_{ST1}$  and  $C_{ST2}$ . At this time frame,  $C_{ST1}$  and  $C_{ST2}$  is individually charged negative and positive data as shown paths in (3), (4) in Fig. 11(a), respectively. Thus,  $C_{ST1}$  charged negative data anneals the degradation of driving TFT DTFT1and  $C_{ST2}$  charged positive data results in OLED emission.

Fig. 11. (a) The polarity balanced driving pixel circuit employing a negative bias annealing and (b) Timing diagram for proposed new driving scheme [9].

However, each pixel in the previous work needs 6 TFTs, 2 capacitors and 2 data lines for a negative gate bias annealing only. Therefore, a simple driving scheme for a negative bias annealing would be desired.

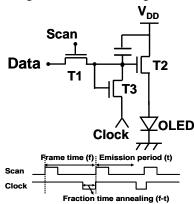

Fig 12. The simple negative bias annealing pixel and a timing diagram.

The negative bias comes from a clock signal line during a fraction of each frame in order to reduce  $V_{th}$  shift of T2. The driving scheme is entitled as "fraction time annealing (FTA)". Fig. 12 shows a FTA driven pixel [10]. When a clock signal is larger than a data voltage, T3 is turned off because  $V_{GS\_T3}$  is 0V. T2 can supply  $I_{OLED}$  according to the input data voltage so that  $V_{th}$  of T2 increases due to a positive gate and drain bias stress. When a clock signal is low, T3 is turned on so that a gate node voltage of T2 would be discharged to the low state of clock signal. The negative bias of the clock signal is applied to the gate node of T2 so that the holes are trapped in  $SiN_x$  insulator, so that an increased  $V_{th}$  of a-Si:H TFT due to the positive gate and drain bias is

reduced considerably. Although  $I_{OLED}$  stability in the negative bias annealed pixel is improved compared with conventional one, a gradual decrease of  $I_{OLED}$  in the negative bias annealed one may be attributed to the small  $\beta$  of a negative gate bias stress compared with  $\beta$  of a positive gate bias stress ( $\Delta V_{th} = A \times t^{\beta}$ ).

### 3. Conclusion

We discuss a highly stable TFT pixel employing both LTPS and a-Si for AMOLED.

ELA (excimer laser annealing) LTPS-TFT pixel should compensate  $I_{OLED}$  variation caused by the non-uniformity of LTPS-TFT due to the fluctuation of excimer laser energy and amorphous silicon TFT pixel is desired to suppress the decrease of  $I_{OLED}$  induced by the degradation of a-Si TFT. In order to drive high quality AMOLED, the various compensation schemes of both LTPS and a-Si TFT are discussed.

### 4. References

- [1] R. Dawson et al, IEEE IEDM, pp.841-851,1998.

- [2] S.H.Jung et al, IEEE EDL, vol.25, p.690,2004.

- [3] S.M.Choi et al, SID Digest, pp.260-263, 2004

- [4] T. Sasaoka et al, SID Digest, pp.384-386, 2001

- [5] J.H.Lee et al, IEEE IEDM, pp. 953-956,2005

- [6] J.C.Goh et al, IEEE EDL, vol.24, pp.583-585, Sep. 2003.

- [7] J.H.Jung, SID Digest, pp.1538-1541, 2005.

- [8] A.Nathan et al, IEEE JSSC, vol.39, p.1477, 2004.

- [9] B.H.You et al, SID Digest, pp.275-278, 2004.

- [10] J.H.Lee et al, IDW 2005, pp.667-670, 2005.

- [11]K.S.Karim, IEEE EDL, vol.25, pp.188-190, April 2004.