## Improvement of Defect Detection in TFT-Array Panel

# Kyo Young Chung YieldBoost Tech, Inc., San Jose, California, U.S.A.

#### Abstract

This paper shows hat the defect detection in TFT-array panel can be improved by using newly developed software solution without adding additional hardware instruments. Some issues are reviewed in current TFT array test and new algorithm is explained for detecting more real defects without paying the penalty of reporting more false defects in TFT array test.

#### 1. Introduction

In manufacturing of TFT-LCDs, the TFT-array base plates are functionally tested by TFT-array test equipment when their TFT-array fabrication process has been completed [1-3]. Each TFT-array panel is functionally tested for its defect detection and repaired if there are any defects detected, before the TFT-array base plates are sent to next process step for cell assembly. It is very important to have high yield in cell and module inspections since expensive materials are added in the cell and module assembly processes. Recently, it was shown that the profit of TFT-LCD manufacturing can be maximized by optimizing the parameters of TFT-array test [4]. The profit maximization was performed by finding the test parameters making the right balance between the improvement of cell and module yields and the cost reduction of TFT-array repair. In order to achieve high cell or module yield, one needs to have accurate defect detection at TFT-array test equipment and effective work at TFT-array repair equipment. Ideally, TFT-array test equipment is supposed to report all the defective pixels in the TFT-array panel without reporting normal pixels as defective pixels. However, in reality, TFT-array test equipment may miss real defects, which are called leaked or under-killed defects, and wrongly report normal pixels as defective pixels, which are called false or over-killed defects. In this paper, the causes for the under-killed and overkilled defects are reviewed based on the analysis of the measurement noise of TFT-array test system, defect signal variation, and thresholding scheme for defect determination, and then novel methodology is introduced to reduce the under-killed and over-killed defects.

## 2. Current Issues of TFT-array Test

### 2.1 Measurement Noise

In TFT-array test, the storage capacitor of each pixel is charged first and then its signal from the stored charge is measured after charge holding time period. For example, the pixel voltage, which is the voltage potential on the surface electrode of the storage capacitor or ITO electrode, is measured to test the functionality of every pixel circuit [1]. When the pixel voltage is measured for every pixel, it is normally modified by noise that is originated from the measurement system. Thus the collected data of measured pixel voltages comes to have certain statistical distribution.

### 2.2 Defect Signal Variation

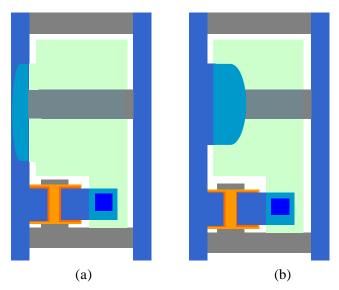

There are many types of defects in TFT-array panel. Some defects such as the overlap between date line and ITO electrode as shown in Figure 1 can give measured pixel voltage whose magnitude varies depending on the severity of such defects i.e. the overlapped area of ITO and data line.

Figure 1. Overlap between data line and ITO.

(a) Deformed ITO pattern over data line. (b) Deformed data line under ITO

## 2.2.1 Signal Variation in Display Operation

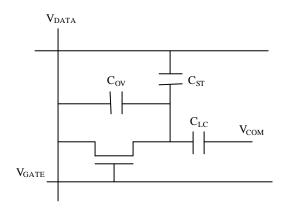

The presence of overlapped area of ITO and data line usually decreases  $V_{LC}$ , the voltage across the liquid crystal layer, and causes the wrong gray level in the display operation. The decrease of  $V_{LC}$  is caused by the crosstalk of the data signal through capacitive coupling of the overlapped area of ITO and data line. Figure 2 shows the electrically equivalent circuit of the pixel with an overlap defect between date line and ITO electrode.

Figure 2. Equivalent circuit of the pixel with an overlap defect between date line and ITO electrode where  $C_{\text{ov}}$ ,  $C_{\text{ST}}$ , and  $G_{\text{LC}}$  indicate the overlap, storage, and liquid crystal capacitance, respectively.

In case of the dot inversion driving scheme, the amount of decrease of  $V_{\rm LC}$  denoted by ?  $V_{\rm LC}$  is given by

$$?V_{LC} = ?V_{DATA} C_{OV} / 2 (C_{ST} + C_{LC} + C_{OV})$$

(1),

where  $?V_{DATA}$  denotes the amount of average change of  $V_{DATA}$  at its polarity change.

Thus the change of gray level is given by  $?V_{LC}$  and its magnitude is proportional to the overlapped area of ITO and data line since  $C_{OV}$  is also proportional to the overlapped area.

### 2.2.2 Signal Variation in TFT-array Test

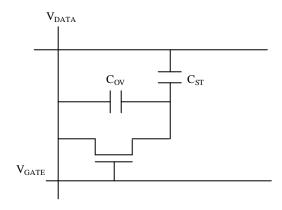

When TFT-array panel is tested by an array tester, for example using voltage imaging <sup>TM</sup> [1], the electrically equivalent circuit of the pixel with an overlap defect between date line and ITO electrode becomes that

shown by Figure 3 and the pixel voltage on ITO electrode,  $V_{P\ OV}$ , becomes

$$V_{P OV} = V_{DH} - ?V_{DATA} C_{OV} / (C_{ST} + C_{OV})$$

(2)

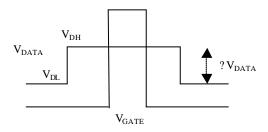

for the driving signals shown in Figure 4, while normal pixels have  $V_{\text{DH}}$  for their pixel voltages.

Figure 3. Equivalent circuit of the pixel with an overlap defect between date line and ITO electrode when TFT-array panel is tested by an array tester.

Figure 4. Driving signal patterns to charge the storage capacitors in TFT-array panel.

Then the defect signal defined as the difference between normal and overlap-defective pixel voltages,  $V_{\rm d\ OV}$ , becomes

$$V_{d OV} = ? V_{DATA} C_{OV} / (C_{ST} + C_{OV})$$

(3).

Therefore the defect signal in an array tester also depends on  $C_{\rm OV}$  and is proportional to the overlapped area of ITO and data line.

Some types of defects such as the metal short between drain and source electrodes of TFT give very distinctive measured pixel voltage and so relatively large defect signals. In case of a short defect between the drain and source electrodes, the pixel voltage becomes  $V_{\rm DL}$ , and its defect signal,  $V_{\rm d~SH}$ , becomes

$$V_{d SH} = V_{DH} - V_{DL} = ?V_{DATA}$$

(4),

which is always constant and larger than that for the overlap defect between date line and ITO electrode.

Thus one can see that the detection of ITO - data line overlap defect at TFT-array test, in many cases, can be very difficult because its defect signal may not be big enough. Some types of defects have large defect signals while other types of defects have small defect signals.

## 2.3 Issues in Thresholding Scheme

As with other test and measurement equipment, TFT-array test equipment has noise in its measurement of the pixel voltages as stated in Section 2.1. And because of the presence of measurement noise, TFT-array test equipment normally sets the lower and upper limits of the pixel voltages to define the pass zone for the measured pixel voltages. The pixels are passed as good when their pixel voltages fall within the pass zone, and reported as the defective pixels when their pixel voltages fall outside the pass zone.

As seen in the previous section, however, there are many types of defects which have a small defect signal and their pixel voltages are not separated from but overlapped with the pass zone. This overlapping of defective pixels and good pixels in the sense of measurement signal causes defective pixels to be regarded as good pixels and missed in a defect report, which is called under-killing or missing the defects.

In order to avoid having under-killed or leaked defects, one can tighten the pass zone. But, then, many good pixels will be reported as defective pixels when their measurement noise is large enough to have the measured pixel voltages fall outside the tightened pass zone, which is called over-killing the normal pixels.

With too many over-killed or false defects, TFT-array test equipment can not generate trustworthy defect files that can be used at TFT-array repair station to locate the found defects. Therefore the setting of the lower and upper limits of the pixel voltages are done to have a reasonable number of over-killed defects with a sacrifice of having under-killed or leaked defects. But having under-killed defects lowers the production yield and becomes a more serious matter as the display size grows.

## 3. Improving Defect Detection Accuracy

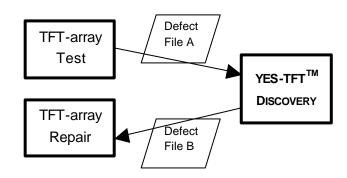

Recently, YieldBoost Tech, Inc. announced, as new methodology to improve production yield of TFT-LCD manufacturing, a yield enhancement software solution YES-TFT<sup>TM</sup>. One of its modules is YES-TFT<sup>TM</sup> DISCOVERY and improves the defect detection accuracy of TFT-array test using Adaptive Thresholding, Cognitive Thresholding, and Flexible Thresholding "[Kyo Y. Chung, under patent application]". In order to apply new methodology in TFT-LCD manufacturing, as shown in Figure 5, YES-TFT<sup>TM</sup> DISCOVERY receives Defect File A from TFT-array test equipment and processes it to generate Defect File B that has more accurate defect data.

For this new scheme to work, Defect File A should be generated by TFT-array test equipment using very tight threshold pass zone and thus has more real defects as well as more false defects, as compared to a defect file generated using regular threshold pass zone. Then YES-TFT<sup>TM</sup> DISCOVERY processes Defect File A, screens out only real defects discarding false defects, and generates Defect File B with improved defect detection accuracy.

Figure 5. Data flow for improving defect detection accuracy using YES-TFT<sup>TM</sup> DISCOVERY.

## 3.1 Adaptive Thresholding

In conventional thresholding scheme, the width of pass zone is determined by two user defined constants, the lower and upper limits of the pixel voltages as described in Section 2.3, and is used for entire production quantity unless the user changes the values of the user defined constants. In Adaptive Thresholding method, the width of pass zone is not constant during TFT-array panel testing and is optimized based on the live information collected from actual measurement data. Therefore the pass/fail criteria adapt themselves to the measurement performance at the time, and separating the real defects from the false defects can be done with improved accuracy.

## 3.2 Cognitive Thresholding

In conventional thresholding scheme, the width of pass zone is determined without considering the probability of defect occurrence. The defect-occurring probability becomes important when there are multiple defects gathered together. In Cognitive Thresholding method, the width of pass zone is adjusted taking the defect-occurring probability into consideration when there are multiple defects in close proximity. Thus the pass/fail criteria modify themselves to the defect-occurring probability at the measurement location at the moment of test, and separating the real defects from the false defects is further improved

## 3.3 Flexible Thresholding

With conventional TFT-array test methodology, there are often incidents of too many defects reported. This can happen due to process contamination, nonuniform thin film layer quality, or unstable operation of TFT-array test equipment. When this happens, detecting real defects and repairing them become practically impossible. In Flexible Thresholding method, the width of pass zone is adjusted with the occurrence of too many defects reported and the number of reported defects is reduced to a number equal to or less than a user defined parameter. Adjusting the width of pass zone is performed in such a way that only real defects are reported without reporting false defects. Thus even in the abnormal cases of too many reported defects due to unstable operation of TFT-array test equipment, detection of

real defects becomes possible without many false defects and repairing real defects become practicable.

## 3.4 Application of New Methodology

In order to achieve the desirable performance of new methodology, Defect File A should have more reported defects resulted from tighter pass zone compared to normal pass zone. Defect File A also needs to have some local information related to the measurement of pixel voltages. Such information includes the measured pixel voltage and row/column number of each defective pixel, local site modal pixel voltage, and local site standard deviation. For the best performance of new methodology, YES-TFT<sup>TM</sup> DISCOVERY shown in Figure 5 needs to receive from TFT-array test equipment the measurement data for the entire pixel voltages and the boundary row/column number for each local site in order to generate all the necessary data required in the process of YES-TFT<sup>TM</sup> DISCOVERY.

## 5. Acknowledgements

Authors would like to express their deep, sincere appreciation to Production Engineering Group of Samsung Electronics LCD Business for allowing and cooperating for the technical demonstration of new methodology reported in this paper.

### 6. References

- [1] G. D. Houser, F. J. Henley. "In-process testing of LCD panels by voltage imaging ™ methods and capabilities", Proc. of the 13th Int. Disp. Research Conf. Eurodisplay 1993, p. 381-384

- [2] M. Brunner, R. Schmid, R. Schmitt, D. Winkler. "In-Process Flat-Panel-Display Testing with Electron Beams", Society for Information Display (SID) Digest 1994, p. 755-758

- [3] L. C. Jenkins, R. J. Polastre, R. R. Troutman, R. L. Wisnieff. "Functional testing of TFT/LCD arrays", IBM J. RES. DEVELOP. VOL. 36 NO. 1 JANUARY 1992, p. 59-68

- [4] Kyo Y. Chung. "Profit Maximization of TFT-LCD Manufacturing by Optimizing TFT-Array Test Parameters", Society for Information Display (SID) Digest 2003, p. 366-369