# Single-Scan Plasma Display Panel(PDP)를 위한 고속 어드레스 에너지 회수 기법

A High Speed Address Recovery Technique for Single-Scan Plasma Display Panel (PDP)

이 준 영

## Jun-Young Lee

Abstract - A high speed address recovery technique for AC plasma display panel(PDP) is proposed. By removing the GND switching operation, the recovery speed can be increased and switching loss due to GND switch also becomes to be reduced. The proposed method is able to perform load-adaptive operation by controlling the voltage level of energy recovery capacitor, which prevents increasing inefficient power consumption caused by circuit loss during recovery operation. Thus, the technique shows the minimum address power consumption according to various displayed images, different from prior methods operating in fixed mode regardless of images. Test results with 50" HD single-scan PDP(resolution = 1366×768) show that less than 350ns of recovery time is successfully accomplished and about 54% of the maximum power consumption can be reduced, tracing minimum power consumption curves.

Key Words : PDP, Energy recovery, Addressing

#### 1. Introduction

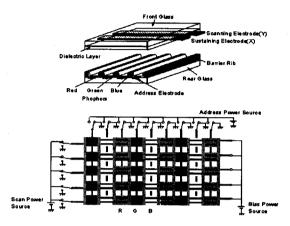

Many kinds of digital display have been developed to meet the market requirements but PDP takes an advantage over other flat panel display(FPD) by the wide view angle, large screen, high brightness, and thinness[1]. Thanks to the attractive merits, PDP is expected to widen its market share in the digital display market. Fig. 1 shows the simplified PDP structure with three electrodes and matrix cell structure. It consists of two glass plates with chemically stable rare gases filled between them. The scanning and sustaining electrodes are built on the front glass, which is coated with dielectric layer and the addressing electrode is on the rear glass. A desired color light can be obtained by exciting the phosphors on the addressing electrode to emit visible light with the ultraviolet photons generated by gas discharge[2]. The PDP cell structure naturally forms capacitances among three electrodes and it causes heating problem of switching devices. Therefore, an energy recovery circuit should be developed in order to save power consumption of address drive ICs. The half-resonant method that is similar to sustain driver suggested by L.F. Webber et. al. and quarter-resonant method have been adopted by most of the PDP makers. Power consumption is successfully reduced with the help of these methods but they cannot be applicable to PDPs requiring a high speed addressing such as large size and high resolution PDPs or single—scan PDPs, due to their slow recovery speed and circuit loss. Another simple method to reduce heat stress is proposed by Y. Sano et. al[3]. It is very simple structure using only resistor but excessive heat dissipated from resistor cannot be accommodated by larger size PDPs.

In this paper, a new address energy recovery technique with fast recovery operation for AC PDP is proposed. This method has load-adaptive power saving with the help of charge-pumping characteristic. operation, which makes it possible to consume the minimum address powers according to various images by controlling the voltage level of recovery capacitor. The load-adaptive operation is desirable characteristic since energy recovery operation may not give a help to power saving at small data switching images whose address powers are dissipated mostly by circulating current for energy recovery rather than data switching. Prototype circuit has been designed and experimented for 50"HD single-scan PDP to show the validity of the proposed circuit.

# II. Mode analysis

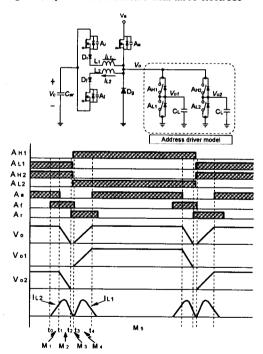

Fig. 2 is the proposed fast address energy recovery circuit(AERC) with address drive IC model at

\*\*\*正 會 員: 檀國大學 電子工學科 專任講師·工博

저자 소개

heavy data switching pattern. It has separate recovery path to reduce switching loss of recovery switches. GND switch is replaced by diode only for GND clamping to save recovery time and switching loss. At white dot on/off image that produces the most address power consumption in practice, the address data switching occurs at each scan line and all capacitances existing among three electrodes are applied. In this case, address drive ICs can be modeled by four switches of  $A_{HI}$ ,  $A_{LI}$ ,  $A_{HI}$ , and  $A_{LI}$ , as shown in Fig. 5, and the load capacitance  $C_L$  can be written as

$$C_L = \frac{N_d}{N_M} \left( \frac{1}{2} C_{b,line} + \frac{1}{3} C_{a,line} \right) \tag{1}$$

where  $N_M$  is the number of recovery circuit blocks. The key waveforms of the proposed method with this address driver model are depicted together in this figure and the mode diagrams of proposed method are shown in Fig. 3. Before the mode explanation, it is assumed that paramitic components of switching devices are ignored and  $L_1 = L_2 = L$ . Mode 1  $(t_0 \le t < t_1)$ : Mode 1 begins at  $t_0$  when  $A_r$  is turned on. Since  $A_s$  switch is already maintained as conducting state, there forms current path including  $A_s$ ,  $L_2$ ,  $D_f$ , and  $A_f$  in sequence. Accordingly,  $I_{L,2}$  linearly is increased with the slope of  $(V_s - V_c)/L$  to store the magnetic energy in the inductor  $L_2$ . The current is expressed as

$$I_{L2} = \frac{V_a - V_c}{L} (t - t_0). \tag{2}$$

The current built up before the energy charged in panel capacitances is recovered helps to reduce transition time from  $V_a$  to zero and, thus, increase the energy recovery speed. By minimizing recovery time, address pulse width that is necessary for address discharge is ensured as long as possible. In addition, since this build—up current can be used for the voltage level control of recovery capacitor, recovery operation becomes different according to load condition.

Mode 2  $(t_1 \le t < t_2)$ : When  $A_s$  is turned off, the current built up during mode 1 flows through  $C_L$ ,  $L_2$ ,  $D_f$ , and  $A_f$  in sequence. The resonant current caused by panel capacitance starts to flow and the terminal voltage  $V_o$  goes down from  $V_s$  to zero. During this mode, the equations of  $I_{L2}$  and  $V_y$  are written as:

$$I_{L2} = I_{L2}(t_1)\cos\omega_c(t-t_1) + \frac{V_a - V_c}{Z}\sin\omega_c(t-t_1),$$

(3)

$$V_{o} = V_{c} + (V_{a} - V_{c})\cos\omega_{c}(t - t_{1}) - ZI_{L2}(t_{1})\sin\omega_{c}(t - t_{1})$$

(4)

where

$$Z = \sqrt{\frac{L}{C_L}}$$

and  $\omega_c = \frac{1}{\sqrt{LC_L}}$ .

Mode 3 ( $t_2 \le t < t_3$ ): After mode 2, the diodes of  $D_g$  is turned on and Vois clamped by GND level. Accordingly, the current  $I_{L2}$  starts to flow through  $D_g$ ,  $D_f$ ,  $L_2$ , and  $A_f$ .  $I_{L2}$  is ramped down to zero with the slope of  $V_c/L$  and it can be written as follows:

$$I_{L1} = I_{L1}(t_2) - \frac{V_c}{I}(t - t_2) \tag{5}$$

If data switching happens during  $V_o$  is maintained as around GND level, switching losses of data drive ICs, which should be dissipated by heat, can be reduced.

Mode 4 ( $t_0 \le t < t_0$ ): After  $I_{L2}$  is reduced to zero, the current starts to flow to  $C_1$  through  $A_r$ ,  $D_r$ ,  $L_1$ , and  $A_{H1}$  because  $A_r$  is already turned on during mode 3. The terminal voltage  $V_o$  goes up from zero to  $V_s$ . Similar to eqs. (3) and (4) in mode 2,  $I_{L1}$  and  $V_o$  can be written as

$$I_{L2} = \frac{V_c}{Z} \sin \omega_c (t - t_3), \qquad (6)$$

$$V_o = V_c \left( 1 - \cos \omega_c \left( t - t_3 \right) \right). \tag{7}$$

Mode 5  $(t_s \le t < t_s)$ : After increasing the terminal voltage of address drive ICs increase to  $V_s$ , the rest of magnetic energy of  $L_I$  starts to be recovered toward address voltage source through  $A_r$ ,  $D_r$ ,  $L_I$ , and the body diode of  $A_s$  and it makes the ZVS condition of  $A_s$  and  $A_g$ . During this mode,  $I_{LI}$  decreases to zero with the slope of  $(V_c - V_s)/L$ , which is expressed as

$$I_{L1} = I_{L1}(t_4) + \frac{V_c - V_s}{L}(t - t_5)$$

(8)

When  $A_s$  is turned on to induce address discharge, mode 1 starts again.

## III. Operational characteristics

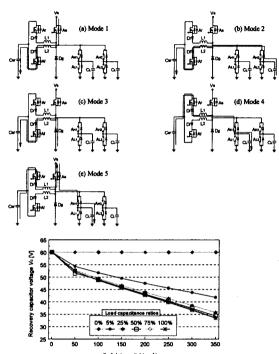

To realize an image, all channels of address drive IC generate data and their switching numbers are changed from zero to the number of scan lines. The energy recovery capacitor voltage level  $V_c$  is important factor to control recovery operation. This level is controlled by the build-up current explained in mode 1, which would make  $V_c$  tend to maintain a higher voltage level than  $V_a/2$ . For instance, while address recovery circuit comes into no load condition, i.e, no address data condition, there exits only build-up current flowing into energy recovery capacitor. In this case,  $V_c$  eventually increases to  $V_a$  and the recovery operation cannot be performed anymore. As data gets increased, discharge current from energy recovery capacitor becomes increased and it makes  $V_c$  lower to some voltage level. Accordingly, the energy stored in panel capacitor starts to be recovered by address recovery circuit. At small data switching images, operation may not give a help to save power consumption because the inefficient power consumption caused by circulating current for recovery operation is larger than that caused by data switching. Therefore, this operation is desirable load-dependant recovery minimize address power consumption. characteristic to of  $V_c$  can be The expression determined power-balancing condition of recovery capacitor during

recovery operation, which is written as

$$\int (i_{charge} \times v_c) dt = \int (i_{discharge} \times v_c) dt$$

(9)

Using this concept, the expression of  $V_c$  can be obtained as

$$V_{c} = \left(1 - \sqrt{\frac{(N_{s} - N_{1})C_{L}}{N_{s}T_{b}^{2}/2L + N_{1}C_{L}\left(1 + \sqrt{1 + \left(T_{b}/\sqrt{LC_{L}}\right)^{2}}\right)}}\right)V_{a}$$

(10)

where,  $N_s$  is the number of total scan electrodes and  $N_I$  is the number of scan electrodes that address data exist on, Also, The current build—up time  $T_b$  is defined as  $t_I-t_0$ . The recovery capacitor voltage is the function of circuit parameters and load conditions. According to load applied to recovery circuit  $C_L$  and  $N_I$ , Calculated  $V_c$  with eq. (10) is in Fig. 4. As  $N_I$  and  $C_L$  are increased,  $V_c$  level becomes lowered. That is to say that while ineffective energy dissipated by address dive ICs is saved when heavy data switching occurs, recovery operation can be minimized in case of small data switching images at which power consumption caused by recovery operation is larger than data switching.

#### IV. Recovery time $T_R$

To determine address recovery time  $T_R$  defined by sum of falling transition time  $T_I$  and rising transition time  $T_I$ , it is necessary to express the transition time between GND and  $V_s$  as the function of design parameters. The falling transition time  $T_I$  defined by  $t_2-t_I$  is obtained from eq. (4) by replacing  $V_o$  with zero. However,  $V_c$  varies according to load changes and it causes that  $V_o$  may not go down to zero. Thus, this definition of  $T_I$  can not be applicable to all load conditions. Fortunately,  $t_2-t_I$  is nearly equal to  $t_3-t_I$  which is defined by the time during which  $I_L$  goes down to zero and it can be used for all load conditions. Therefore, using eq. (3),  $T_I$  can be approximately expressed as follows:

$$T_f = \sqrt{LC_L} \left[ \pi - \tan^{-1} \left( \frac{ZI_{Lo}}{V_a - V_c} \right) \right]$$

(11)

where  $I_{Lo} = (V_a - V_c)T_b/L$ . Assuming that the circuit does not contain any parasitic components, the rising transition time  $T_r$  is same as eq. (12). Since the transition time of this proposed method is the function of  $T_b$  as well as L, the pulse rising and falling times can be shortened by adjusting  $T_b$ . It helps to widen the address discharge time by minimizing the time required by recovery operation.

### V. Experimental results

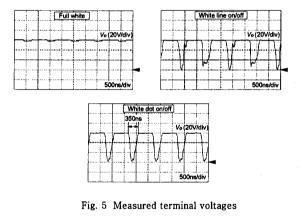

A prototype circuit of the proposed method has been designed for 50" HD single-scan PDP with specifications of Address voltage  $V_s = 60$ V, total

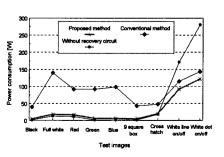

recovery time  $T_R = 350$ ns, and max. load capacitance per one circuit block  $C_L=28$ nF. Key design parameters of  $L=0.1\mu H$  and  $T_b=20 ns$  has been chosen under considering that too small values of L is not difficult to design and too large build-up time may cause a power loss of circuit due to large circulating current. Measured terminal voltages according to data switching are shown in Fig. 5 and less than 350ns of recovery time is successfully accomplished. As explained before, full white image which does not require a heavy switching makes the recovery operation stop automatically and heavy data switching images such as white line on/off and white dot on/off images lower the energy recovery capacitor voltage so that the energy charged in capacitance can be recovered. Fig. 6 shows the power consumption comparisons according to address energy recovery methods. It shows that conventional series LC resonant type reduces well at heavy switching images but dissipates inefficient power caused by circulating current at small switching images. On the other hand, the proposed method can trace the consumption minimum power curve owing load-adaptive operation. Thus, at small data switching address power consumptions characteristic similar to the case without recovery circuit and, at heavy switching patters, address power can be saved like conventional recovery method. The measured data shows that above 54% of address power can be reduced.

## VI. Conclusions

In this paper, a high speed address recovery technique for AC plasma display panel is proposed. By controlling the voltage level of energy recovery capacitor, the proposed method has load—adaptive characteristic that shows minimum address power consumption according to displayed images. In addition, recovery speed can be increased by saving the GND hold time because this method does not use GND switch operation. Prototype circuit has been implemented for 50" HD single—scan PDP and six blocks was designed to drive overall panel. Test results show that less than 350ns of recovery time is successfully accomplished and the maximum power consumption can be reduced from 280W to 130W.

## References

[1] A. Sobel, "Plasma Displays,"IEEE Trans. on Plasma Science, vol. 19, no. 6, pp. 1032-1047, December, 1991.

[2] H. Hirakawa, T. Katayama, S. Juroki, H. Nakahara, T. Nanto, K. Yoshikawa, A. Otsuka, and M. Wakitani, "Cell Structure and Driving Method of a 25-in(64cm) Diagonal High-Resolution Color ac Plasma Display," Poc. Sym.

Society for Information Display, vol. 29, pp. 279-282, 1998.

[3] Y. Sano, A. Takagi, T. Kawada, H. Inoue, and K. Kariya, "Reduction of Power Consumption in Address Driver ICs for PDP by Power Distributing Method," SID'01, 1228-1231, 2001.

Fig. 1 Simplified PDP structure with three electrode

Fig. 2 Proposed method with address driver model and its key waveforms

Fig. 3 Operational mode diagram

Fig. 4  $V_c$  changes according to load capacitance and number of data switching at  $V_a = 60$ V

Fig. 6 Address power consumption comparisons