# 저온 공정에 의한 a-Si:H/c-Si 이종접합 태양전지 제조 및 동작특성 분석

임 충현<sup>1)</sup>, 이 정철<sup>1)</sup>, 전 상원<sup>1)</sup>, 김 상균<sup>1)</sup>, 김 석기<sup>1)</sup>, 김 동섭<sup>2)</sup>, 양 수미<sup>3)</sup>, 강 희복<sup>3)</sup>, 이 보영<sup>3)</sup>, 송 진수<sup>1)</sup>, 윤경훈<sup>1)\*</sup>

# Process and Performance Analysis of a-Si:H/c-Si Hetero-junction Solar Sells Prepared by Low Temperature Processes

Chung Hyun Lim<sup>1)</sup>, Jeong Chul Lee<sup>1)</sup>, Sang Won Jeon<sup>1)</sup>, Sang Kyun Kim<sup>1)</sup>, Seok Ki Kim<sup>1)</sup>, Dong Seop Kim<sup>2)</sup>, Sumi Yang<sup>3)</sup>, Hee Bok Kang<sup>3)</sup>, Bo young Lee<sup>3)</sup>, Jinsoo Song<sup>1)</sup> and Kyung Hoon Yoon<sup>1)\*</sup>

Key words: Hetero-structure(이종 접합), c-Si(단결정 실리콘)

Abstract: In this work, we investigated simple Al/TCO/a-Si:H(n)/c-Si(p)/Al hetero-junction solar cells prepared by low temperature processes, unlike conventional thermal diffused c-Si solar cells. a-Si:H/c-Si hetero-junction solar cells are processed by low temperature deposition of n-type hydrogenated amorphous silicon (a-Si:H) films by plasma-enhanced chemical vapor deposition on textured and flat p-type silicon substrate. A detailed investigation was carried out to acquire optimization and compatibility of amorphous layer, TCO (ZnO:Al) layer depositions by changing the plasma process parameters. As front TCO and back contact, ZnO:Al and Al were deposited by rf magnetron sputtering and e-beam evaporation, respectively. The photovoltaic conversion efficiency under AM1.5 and the quantum efficiency on 1 cm² smaple have been reported. An efficiency of 12.5% is achieved on hetero-structure solar cells based on p-type crystalline silicon.

#### 1. Introduction

The a-Si:H/c-Si heterojunction(HJ) solar cells are getting attention for low cost and high efficient solar cells for its simplicity in structure and process unlike conventional c-Si solar cells. Recently, Sanyo has presented a 100cm<sup>2</sup> large cell of the hetero-structure with an efficiency of 21.2%. (1) HJ solar cells(n-type a-Si:H/p-type c-Si) of a very simple cell structure

have been fabricated on various substrates.

1) 한국에너지기술 연구원 태양전지 연구센터

\*E-mail: <u>y-kh@kier.re.kr</u>

Tel: (042)860-3410 Fax: (042)860-3739

2) 세종 대학교

E-mail: dskim@sejong.ac.kr Tel: (02)3408-3725 Fax: (02)3408-3329

3) LG Siltron

E-mail: excelbeauty@lgsiltron.co.kr Tel: (054)470-6077 Fax: (054)470-6283 A photovoltaic conversion efficiency of 15.3% has been achieved on textured CZ silicon on an area of  $1 \text{ cm}^2$  and 14.8% on an area of  $39 \text{ cm}^2$ .

One of the advantages of HJ solar cells, the low process temperatures, is on the other side on of its biggest disadvantages. (2) But 1 ow temperature fabrication process allows the use of thin c-Si substrate. Another advantage, the very low thickness of the amorphous silicon layers ensure no light degradation as in the case of purely a-Si:H solar cells. (3)

In this work, we investigated in detail process of Al/TCO/a-si:H(n)/c-Si(p)/Al and compared the I-V characteristics and external quantum efficiency(E,Q.E) of HJ solar cells with textured and flat crystalline silicon substrate. Moreover, we investigated reflectance of various TCO layers (ZnO:Al) deposited by PECVD.

# 2. Experimental

# 2-1. Solar cell structure and process scheme

a-Si:H(n)/c-Si(p) hetero-junction solar cells have been fabricated on a 2.0-2.5  $\Omega$  \*cm monocrystalline CZ silicon with the simple process scheme presented below.

- \* substrate cleaning & 1% HF

- \* Al evaporation on the backside

- \* drop of 1% HF on the front-side

- \* PECVD a-Si:H(n) deposition

- \* TCO deposition

- \* Front contact metallization

- \* Protection of the front-side

- \* TCO wet etching & a-Si:H(n) dry etching

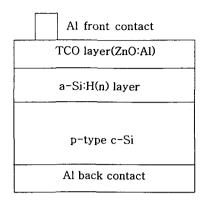

The result of cell structure is shown Fig.1.

Fig. 1 Schematic drawing of the cell structure

Texturization was done after cleaning & 1% HF etch. The protection of the front-side was used photolithographic methods and it determined the cell area (1cm<sup>2</sup>). Silicon surface texturing was conducted by KOH method. (4)

## 2-2. Texturization

Silicon surface texturing is used to minimize reflection losses from the front surface and to enhance optical light-trapping. Anisotropic etching using concentrated alkaline solutions at elevated is often done temperatures semiconductor industry to thin or pattern single-crystal silicon wafers. Relatively alkaline mild solutions with concentrations (less than 5%) of either (KOH) sodium hydroxide or potassium hydroxide (NaOH) are also used to etch a textured surface of microscopic pyramids on silicon substrates with <100>-oriented sur faces. (4)

Fig. 2 SEM photograph for trial at 70°C,

for 30 minutes with 1.5% KOH, 3.8% IPA, and mechanical mixing.

Fig. 3 SEM photograph for trial at 70°C, for 30 minutes with 1.5% KOH, 3.8% IPA, and mechanical mixing.

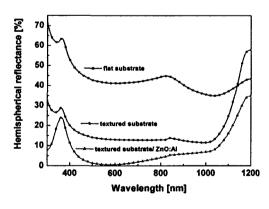

We conducted texturization using KOH method with isopropyl alcohol (IPA) by varying process factors(such as solution temperature, time, KOH and IPA concentration). We obtained two results from the different trials. Two results are shown in Fig. 2, Fig. 3, respectively. And Fig. 4 shows the hemispherical spectral reflectance for a flat silicon substrate, and for a substrate with surface texture similar to that in Fig. 3. Addition of a 100-nm ZnO:Al antireflection coating resulted in the bottom curve shown in Fug.

Fig. 4 Hemispherical reflectacne for silicon substrates with and without surface texturing

# 2-3. Amorphous silicon deposition

The a-Si:H silicon has been deposited by PECVD at 13.56 MHz frequency at a temperature of 350°C. The deposition pressure 300 mTorr and the RF power 6 W. The gas flow rate is 5 sccm, 5 sccm, 5 sccm of SiH<sub>4</sub>, PH<sub>3</sub>, H<sub>2</sub> respectively. We investigated *Voc*, *Jsc*, *FF* by varying deposition time(3min - 4min) Fig.5 shows *Voc*, *Jsc*, *FF* with different deposition times of a-Si:H on textured silicon substrates.

Fig.5: Voc. Jsc. FF with different deposition times

# 2-4. TCO deposition

Currently, two different materials were used: Zincoxide (ZnO) and Indium Tin Oxide (ITO) as TCO deposition. Each material has its specific advantages and disadvantages. The main disadvantage of the ITO is that it is a very expensive material. However, ITO layers have good conductivity even when deposited at room temperature. Oppositely, ZnO is much cheaper than ITO but has not

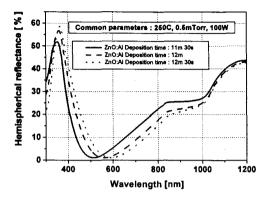

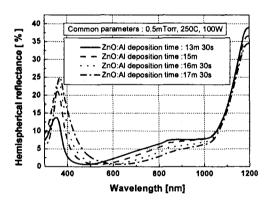

such a good conductivity. (2) Aluminium doped (ZnO:Al) was deposited by RF-sputtering by changing deposition time. Fig. 6, 7 shows the results of hemispherical reflection measurements on flat and textured crystalline silicon substrates.

Fig. 6: Hemispherical reflectance of ZnO:Al on flat crystalline silicon substrate.

Fig. 7: Hemispherical reflectance of ZnO:Al on textured crystalline silicon substrate.

# 2-5. TCO deposition

Aluminium was used as the back and front contact metal. Front metal was evaporated using shadow mask consisted one busbar (200-um thick) and 11 fingers, which its shadow factor is 9.2%. The height of the fingers and the busbar was 2um.

# 3. Results and discussion

In the Fig. 2, 3, the height of pyramids on textured silicon substrate was changed by temperature on solution. In the Figure 5, we noticed lower *Voc* values when amorphous silicon was deposited during 2 minutes. The reason for this is that shunt resistance is happened between amorphous silicon and crystalline silicon substrate due to the higher height of pyramids. However, it has higher *Jsc* due to reduced recombination velocity on the region of short wavelength. Fig. 7 shows less than 5% reflectance over most of useful spectrum.

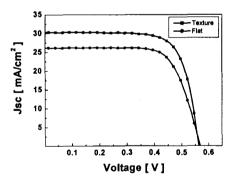

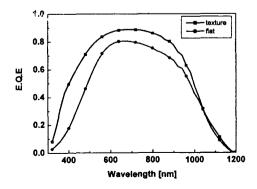

Fig. 8 shows illuminated I - V characteristics and external quantum efficiency for fabricated hetero-structure solar cells on textured and flat crystalline silicon substrates. In the Fig. 8, we confirmed lower current densities on the region of long wavelength. In this case, back surface field should be needed in order to reduce recombination velocity.

|         | <i>Voc</i><br>[V] | Jsc<br>[mA/cm²] | <i>FF</i> [%] | Efficiency [%] |

|---------|-------------------|-----------------|---------------|----------------|

| Flat    | 0.56              | 26.14           | 71.5          | 10.5           |

| Textrue | 0.561             | 30.31           | 73.5          | 12.5           |

Fig. 8: Illuminated I - V characteristics and E.Q.E

In this work, we didn't optimize fully amorphous silicon layer, TCO layer, and front grid, so *Voc*, *FF* of fabricated solar cells are a little low. Moreover, interface properties among amorphous layer, crystalline layer, and TCO layer should be investigated by adapting analytical equipment.

## 4. Conclusion

12.5% (AM1.5.  $1 cm^2$ . 25°C) high conversion efficiency in a fabricated hetero-structure solar cell with low temperature was achieved. The cell has a short circuit density ( Jsc) of 30.31 mA/cm<sup>2</sup>, an open circuit voltage ( Voc ) of 0.561V, and a fill factor ( FF ) of 73.5%. In this work, we didn't investigate about BSF and intrinsic silicon layer. For the high conversion efficiency, more specific studies should be conducted..

### References

- [1] T. Sawada et al.: Conf. Record of the IEEE First World Conf. on Photovoltaic Energy Conversion, Hawaii 1994, p.

- [2] Dietmar B, Torsten B. Oliver V. "Large Area (n) a-Si:H/ (p) c-Si Heterojunction Solar Cells with Low Temperature Screen PrinTed Contacts", 19<sup>th</sup> European Photovoltaic Solar

- Energy Conference, 7-11 June 2004, Paris .

- [3] M. Tucci, G. de Cesare, Journal of Non-Crystalline Solids 338-340 (2004) "17% Efficiency Heterostructure Solar Cell Based on p-type Crystalline Silicon"

- [4] P. Campbell, et al., "Light Trapping and Reflection Control with Tilted Pyramids and Grooves," 20<sup>th</sup> IEEE PVSC, Sept. 1988, pp. 713-716