# Enhancement of Pattern Fidelity for Metal Layer in Attenuated PSM Lithography by OPC

Hoong-Joo Lee and Jun-Ha Lee

Dept of Computer System Engineering, Sangmyung University, Chonan, 330-720, Korea Tel: +82-41-550-5360 Fax: +82-41-550-5386 E-mail: hjlee@smu.ac.kr

**Abstract:** Overlap errors and side-lobes can be simultaneously solved by the rule-based correction using scattering bars with the rules extracted from test patterns. Process parameters affecting the attPSM lithography simulation have been determined by the fitting method to the process data. Overlap errors have been solved applying the correction rules to the metal patterns overlapped with contact/via. Moreover, the optimal insertion rule of the scattering bars has made it possible to suppress the side-lobes and to get additional pattern fidelity at the same time.

Keyword: ule checking, OPC, PSM, Side-lobes, Simulation, Scattering bars, RET, Overlap errors, Jog filtering

### 1. INTRODUCTION

In the current era of semiconductor fabrication, lithography process technology beyond the conventional resolution limits of the exposure tool is inevitable. A number of resolution enhancement techniques(RET) such as off-axis illumination(OAI), optical proximity correction(OPC), and phase-shifting mask(PSM) are well known and well versatile. Two types of PSM, alternating phase-shifting mask(altPSM) and attenuated phase-shifting mask(attPSM), are typical RETs.

The altPSM enhances the resolution of the gate layer at the cost of design, layout, multi-exposure and reticle manufacturing complexity[1]. The attPSM is well known to be effective in improving the exposure latitude(EL) and the depth-of-focus(DOF) of the patterns such as contact holes and metal lines at the cost of rigorous tuning of the process to make it side-lobes and side-rings free[2-4]. The side-lobe printing is the biggest challenge in the attPSM, which depends on the pattern and lithography parameters such as feature size, pattern density, pitch, and transmission[4-5].

Chrome(Cr) pattern generation, which is the existing method to prevent side-lobes, requires lithography engineer's experience as well as additional fabrication steps for Cr pattern generation on the mask[6-8]. Increase of the partial coherence has been another solution, but it might bring about a low DOF in the case of contact holes[9-10].

In the back-end lithography process for the metal layer, especially for system VLSI circuits, overlap errors come from line-end shortening, corner rounding, tight margin between metal and contact/via, and misalignment. The overlap error causes the process failure such as bridging and insufficient overlapping between contact and metal layers.

Therefore, two problems, side-lobes and overlap errors must be solved at the same time, when attPSM is applied to the metal layer lithography. Besides, the side-lobe phenomena can be more serious, when the optical proximity correction is applied to the metal layer to provide enough overlap margin compensated for overlap errors by misalignment.

In this paper, an OPC methodology using scattering bars, which requires the relatively simple process compared to the Cr shield method, has been presented to solve simultaneously the problems mentioned above. Oversizing the metal pattern to ensure the overlap margin has been followed by the scattering bar OPC. Design rule checking(DRC) and rule generation for scattering bar insertion has been performed in the middle of correction flow.

### 2. SIDE-LOBE AND OVERLAP ERROR

The resolution of the optical lithography system can be expressed by Rayleigh relation,  $R = k1 * \lambda / NA$ , where  $\lambda$  is a wavelength, NA is the numerical aperture, and k1 is a factor depending on the lithography system as well as resist chemistry[11]. It is obvious that shorter exposure wavelengths lead to better image resolution. It is also clear that lenses with higher NA also achieve better resolution. Resolution enhancement techniques including OPC and PSM can improve the resolution without the change of  $\lambda$  or NA in the lithography system. The RET is also effective to improve the depth-of-focus defined by the following equation,  $\delta = k2 * \lambda / (NA)^2$ , where k2 is a constant.

The cause of the side-lobe printing in the attPSM lithography can be explained as follows. In case of a binary intensity mask, there is no background field, hence the side-lobe intensity is just the square of the electric field caused by discontinuity at the pattern However, in attPSM, there is intended background transmission, and the side-lobe intensity is the square of the sum of electric field amplitude caused by discontinuity plus the background electric field. Hence, the side-lobe intensities in attPSM are much stronger and get printed easily. Not only the various optical process parameters such as numerical aperture, partial coherence and transmission rate but also pattern dependency such as feature size and pitch, does have the influence on the intensity and location of the secondary maxima, which directly related with side-lobe printing problem. For patterns so dense that side-lobes do not form and for patterns so sparse that side-lobes do not interact, a high transmission rate is

desirable for more phase interaction. On the other hand, patterns with intermediate periodicities are the most sensitive to side-lobe printing. Thus, the low level of the transmission rate should be used.

In case of the metal layer lithography process, overlap errors by misalignment must be compensated with the enough overlap margin. To achieve the enough overlap margin, OPC should be applied to the metal pattern. The rule-based OPC rather than the model-based OPC is relatively effective to modify the region of concern in the metal pattern[12]. However, pattern enlargement for the metal pads to get the overlap margin gives rise to the unwanted side-lobe printing. Therefore, the correction to the overlap errors must be performed simultaneously with the suppression of the side-lobes.

In general, SB(scattering bar) has been used the one of the OPC techniques to achieve the better DOF margin[13]. Using SB OPC, both the semi-isolated and isolated features can achieve performance comparable to the dense features. For values of k1 below 0.4, it is widely accepted so that SB OPC is the common enabling factor for the other RETs. SB OPC improves the matching of the diffraction pattern formation of the more isolated features to the dense ones, so that the critical dimension(CD) behavior through focus is similar. Two parameters govern the application of SB OPC: the width of the SB and the SB separation to the main feature edge. Based on the same concept as the SB for the better pattern fidelity around the SB, the possibility that side-lobe printing can be suppressed by applying SBs is stressed in this paper, because the field intensity of the side-lobe can be offset by the intensity in the opposite phase from scattering bars..

## 3. RULE-BASED CORRECTION ALGORITHM AND ANALYSIS

The proposed scattering bar OPC applied to the metal layer lithography using attPSM has shown the better pattern fidelity near around the SB and the two-layer mask structure compared to Cr shield method. Using the rule-based OPC, a sequential correction step of oversizing, cutting, and jog-removing for the metal pattern to ensure the overlap margin has been applied, and then followed by the scattering bar insertion.

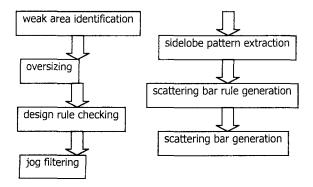

Fig. 1. Correction flow for suppression of overlap errors and side-lobes in AttPSM lithography.

Design rule checking at the each correction step has been performed in the middle of correction flow. Simulation results based on the proposed methodology, side-lobe prints as well as overlap errors induced by misalignment have been effectively removed.

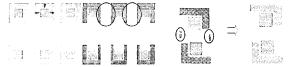

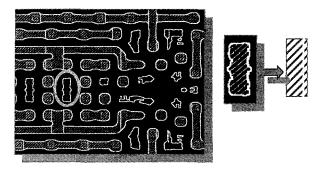

Fig. 1 shows the whole OPC flow for the suppression of overlap error and side-lobe phenomena in the metal layer lithography process. Prior to lithography simulation, first of all, Calibre, the lithography simulator by Mentor Graphics, has been calibrated. Test patterns having design rules same as real SEM data have been designed. The metal layer lithography simulation has been performed with annular-type illumination,  $\sigma$  of outer 0.85,  $\lambda$  of 248nm, NA of 0.68. Although the transmission rate of 0.03 should be a fixed process parameter, in our case, it has been adjusted to express the unexpected real side-lobe patterns occurring in the dense area or large pad patterns of the metal layer. Oversizing the metal pattern, overlapped with contact/via, has been carried out, and the spec value of misalignment of the lithography system has been used as oversizing dimensions. Then, the space margin between patterns have been ensured by properly cutting the oversized patterns with design rule checking(DRC). Jog-filtering has been applied to remove the jogs generated after the cutting step. These successive correction steps for suppression of overlap errors are depicted in Fig. 2(a) to (b). When attPSM is applied to the corrected metal patterns, unwanted side-lobe prints can be removed by the existing Cr shield method. Side-lobe images can be extracted through the aerial image simulation with PrintImage function offered by Calibre from Mentor. The extracted side-lobe patterns must be reshaped rectangularly using EXTENTS function in Calibre to avoid the huge handling time for Cr shield layout data, as shown in Fig. 3. Instead, compared to the Cr shield method, scattering bar OPC presented in this work has made it possible not only to provide the simple two layer mask structure without the Cr layer but also to improve the pattern fidelity near around the scattering bars. To determine the width of the scattering bar to be inserted, aerial image simulation

Fig. 2. (a) oversizing and cutting, and (b) jog filtering.

Fig. 3. Extracted side-lobe patterns and reshaping for the side-lobe patterns after EXTENTS function.

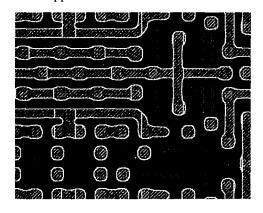

has been done with test patterns. Then, the insertion rules of the scattering bar have been determined with the rule parameters such as the feature size, the scattering bar width, distance between the metal feature and the scattering bar, and the distance between scattering bars themselves. The result of aerial image simulation for the metal patterns with scattering bars inserted is shown in Fig. 4. Although the absolute value of DOF could not have been calculated in our work, the proposed method using scattering bar OPC has given the better pattern fidelity for the metal patterns near around the scattering bars, relatively compared to Cr shield method, as shown in Fig. 5. This method has been also applied and verified to the, so-called, background-clear mask with partially transmitting metal patterns. In this case, the side-lobe prints have been found inside of the metal patterns not outside, as depicted in Fig. 6. To extract side-lobes inside of the metal patterns, HOLES function of Calibre has been used, and then, the same insertion procedure has been applied. Fig. 6 also shows the side-lobe suppression

Fig. 4. Aerial image simulation with scattering bars.

Fig. 5. (a) Cr shield and (b) scattering bar method.

Fig. 6. Side-lobe correction with scattering bars for the background-clear mask patterns.

after aerial image simulation for the background-clear metal patterns.

### 4. CONCLUSION

The proposed scattering bar OPC applied to the metal layer lithography using attPSM has shown the enhanced pattern fidelity and the two-layer mask structure compared to Cr shield method. Using the rule-based OPC, a sequential correction step of oversizing, cutting, and jog-removing for the metal pattern to ensure the overlap margin has been applied, and then followed by the scattering bar insertion. Design rule checking at the each correction step has been performed in the middle of correction flow. Simulation results based on the proposed methodology, side-lobe prints as well as overlap errors induced by misalignment have been effectively removed.

#### References

- G. N. Vandenberghe, P. Jaenen, R. M. Jonckheere, K. Ronse, and O. Toublan, SPIE 4409, p. 61, 2001

- [2] H. Iwasaki, K. Hoshi, and H. Tanabe, SPIE 3412, p. 601, 1998.

- [3] K. Aramaki, T. Hamada, D. K. Lee, H. Okazaki, N. Tsugama, and G. Pawlowski, SPIE 3999, p. 738, 2000.

- [4] N. Singh, and M. Mukherjee-Roy, SPIE 4691, p. 1054, 2002.

- [5] I. B. Hur, J. H. Kim, I. H. Lee, H. E. Kim, C. N. Ahn, K. H. Baik, and S. H. Choi, SPIE 2440, p. 278, 1995.

- [6] C. Dolainsky, P. Karakatsanis, F. Gans, R. Pforr, and J. Thiele, SPIE 4000, p. 1156, 2000.

- [7] H. Iwasaki, K.Hoshi, H.Tanabe, and K. Kasama, SPIE 3236, p. 544, 1998.

- [8] Toublan, N. Cobb, and E. Sahouria, SPIE 4346, p.1541 2001.

- [9] Y. Chen, Y. Wang, and R. Chu, SPIE 3679, p. 812, 1999.

- [10] Z. Lu, Y. Cui, A. Thomas, S. Mansfield, G. Kunkel, D. Dobuzinsky, F. Zach, D. Liu, K. Chen, G. Jordhamo, A. Gutmann, and T. Farrell, SPIE 3678, p. 923, 1999.

- [11] J. Helbert, *Handbook of VLSI Microlithography*, Noyes Publication, p. 472, 1991.

- [12] J. S. Park, D. H. Kim, C. H. Park, Y. H. Kim, M. H. Yoo, J. T. Kong, H. W. Kim, and S. I. Yoo, SPIE 4562, p. 1104, 2002.

- [13] N. Kachwala, J. S. Petersen, J. Chen, M. Canjemi, and M. McCallum, SPIE 3679, p. 55, 1999.