# 수평형 파워 MOSFET에 있어서 트렌치 Isolation 적용에 의한 순방향 항복특성 개선을 위한 새로운 소자의 설계에 관한 연구

김진호, 김제윤, 유장우, 성만영, 김기남',

고려대학교 전기공학과, 삼성전자 메모리 사업부

# The Study of Improving Forward Blocking Characteristics for Small Sized Lateral Trench Electrode Power MOSFET using Trench Isolation

Jin-Ho Kim, Je-Yoon Kim, Jang-Woo Ryu, Man-Young Sung, Ki-Nam Kim\*

Department of Electrical Engineering, Korea University. Memory Division, Samsung Electronics, Co., Ltd.\*

#### Abstract

In this paper, a new small sized Lateral Trench Electrode Power MOS was proposed. This new structure, called LTEMOS(Lateral Trench Electrode Power MOS), was based on the conventional lateral power MOS. But the entire electrodes of LTEMOS were placed in trench oxide. The forward blocking voltage of the proposed LTEMOS was improved by 1.5 times with that of the conventional lateral power MOS. The forward blocking voltage of LTEMOS was about 240 V. At the same size, an improvement of the forward blocking voltage of about 1.5 times relative to the conventional MOS was observed by using ISE—TCAD which was used for analyzing device's electrical characteristics. Because all of the electrodes of the proposed device were formed in each trench oxide, the electric field was crowded to trench oxide and punch—through breakdown was occurred, lately.

Key Words: forward blocking voltage, trench electrode, power MOS, punch-through

### 1. INTRODUCTION

Power semiconductors have been developed steadily into core parts of power sources, power conversion and control in the field of facilities. home appliances, industrial information, communication transportation, with the rapid systems. etc together progress of power electronics industry. The application extent of power semiconductor devices has been widened in combination of a high level of information society as more people have been recently dependent on electric energy. Power semiconductors are being currently used as an application of intelligent power inverters to a refrigerator, a washing machine and a vacuum cleaner as well as core parts of industrial system. As these power semiconductor devices have a field of application. study understanding and improving characteristics individual devices has been made constantly. [1-3]

The forward blocking voltage of semiconductor devices is an important factor in decision on the field of application. When

a device is turned on and we consider a resistance component of the bulk region and the channel region from the viewpoint of breakdown characteristics, low resistance is effective in low power dissipation. However, the forward blocking voltage would become lower due to very low resistance so this device can not be used in the field of application where high voltage is required.

Power MOS devices have a merit of high input impedance, fast switching time, and stability in temperature as well known. Power MOS devices are mainly used as switches in the field of power electronics, the on-state resistance especially breakdown voltage are regarded as the most Power MOS important parameters. devices that enable a small size, a light weight, high-integration and relatively high voltage are required these days.

In this paper, we propose the structure that enables high integration while keeping size the same as the conventional lateral power MOS without extending the structural size for the improvement of the forward blocking electrode structure of The proposed device is changed from that of the conventional lateral power MOS trench oxide and we verify this proposed to the conventional structure is superior structure in the forward blocking characteristics. We verify that the proposed device has the same I-V characteristics and improved forward blocking characteristics in conventional device. comparison with the [4-5]

# 2. DEVICE STRUCTURE AND OPERATION

The channel of the proposed power MOS was formed vertically while that of the conventional one was formed laterally. The

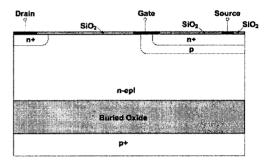

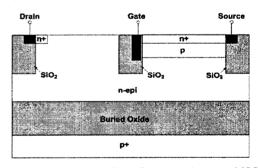

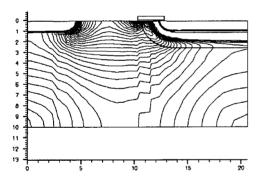

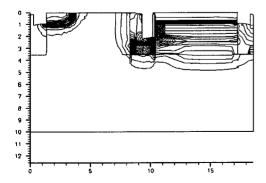

cross—section structures of the conventional lateral power MOS and the proposed one are shown in Fig.1 and Fig.2, respectively. The design parameters for simulation are showing Table.1. The main difference between the conventional lateral power MOS and the proposed one is each electrode structure as shown in Fig.1 and Fig. 2.

Fig.1 The cross-section of conventional lateral power MOS with the conventional electrodes

Fig.2 The cross-section of proposed power MOS with the trench electrodes

| Process Structure Parameter Parameter |                     | Lateral<br>Length | Vertical<br>Depth | Doping<br>Concentration             |

|---------------------------------------|---------------------|-------------------|-------------------|-------------------------------------|

| Drain région                          |                     | 7μm               | 1 <i>µ</i> m      | 1x10 <sup>20</sup> cm <sup>-3</sup> |

| Source region                         |                     | 7μm               | 1 <i>µ</i> cm     | 1x10 <sup>20</sup> cm <sup>-3</sup> |

| n-epi layer                           |                     | 20μm              | 6 <b>µ</b> m      | 1x10 <sup>14</sup> cm <sup>-3</sup> |

| € Gate electrode                      |                     | 0.9µm             | 2.1 µm            | •                                   |

| p-region 🔌                            |                     | 7μm               | 2.1 µm            | $1 \times 10^{16} cm^{-3}$          |

| Gate oxide                            |                     | 1000Å             | •                 | •                                   |

| Channel                               | Conventional device | 1.1 <i>µ</i> m    |                   |                                     |

|                                       | Proposed<br>device  | •                 | 1.1 <i>µ</i> m    |                                     |

| Trench oxide                          |                     | 2 <i>μ</i> m      | 3.5 <i>µ</i> m    | •                                   |

Table.1 Design parameters for simulation

In this paper, The electrode regions of source, drain, and gate were modified into the trench oxide in order to increase the forward blocking voltage of the device. The forward operation of the proposed device was the same as that of the conventional one. When a higher voltage more than the threshold voltage was applied to the gate of the proposed device, electrons that departed from source passed by the channel formed in the right side of the gate electrode. They were injected into the n+ drain region and made the device operate. [6]

The conventional lateral power MOS device that operated on majority carrier had a fast switching speed under no influence minority carrier accumulation. But it did not allow a large current and could not stand at a high voltage. To solve this problem, each electrode of the proposed power MOS was formed in the trench oxide layer so the lateral electric field was all concentrated on the trench oxide. Thus, the proposed small sized device could have a high forward blocking voltage due to this structural advantage. The conventional device did need to have a size of more than 100 um for a forward blocking voltage of more than 200 V but the proposed one has a superior and efficient structure that only did need a small size of 20 um to meet the same condition.

## 3. SIMULATION AND RESULTS

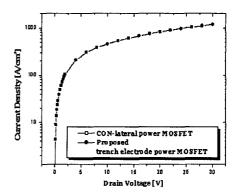

In this paper, the electrical characteristics of the proposed device were investigated by using ISE-TCAD, the 3-D device simulator. When a voltage of 12 V was applied at the gate, the I-V characteristic curves of the MOS conventional and proposed power shown Fig. The devices were in current-voltage characteristics between conventional device and proposed one

almost same as shown in Fig. 3. The voltage of drain and source is applied to measure the breakdown voltage at a gate voltage of 0 V.

Fig.3 The I-V characteristic curves of conventional lateral power MOS and the proposed trench electrode power MOS

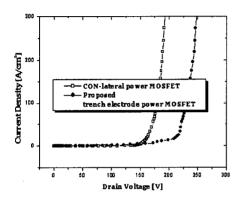

The forward blocking characteristics of the proposed MOS conventional and power devices were shown in Fig. 4. Power MOS devices are used mostly in the field of medium voltage and small current so are not used in high voltage application because the punch-through phenomenon of the a low MOS device occurs structurally at voltage. However, the proposed trench electrode power MOS is designed to have trench electrodes. Thus all of the electric field applied to the inside of the device is concentrated on trench oxide first and as a result, the breakdown occurs at voltage. As shown in Fig. 4, the conventional device has a breakdown voltage of 160 V but the proposed one has that of 240 V which is improved 1.5 times as mush as the conventional ones.

The electric field when breakdown was occurred between the conventional and the proposed trench electrodes power MOS device was shown in Fig. 5 and Fig. 6. As

shown in Fig. 6, the electric field is all concentrated on the trench oxide. Thus, the proposed trench electrode power MOS has a higher forward blocking voltage.

Fig.4 The forward blocking characteristic curves of conventional and proposed power MOS

Fig.5 The electric field distribution of the conventional lateral power MOS

Fig.6 The electric field distribution of the proposed trench electrode power MOS

## 4. CONCLUSION

The lateral trench electrode power MOS was proposed and it was verified by the 3-D device simulator, ISE-TCAD that the power MOS electrically proposed was superior to the conventional lateral power MOS. Especially the proposed power MOS had a breakdown voltage more than 240 V compared to that of the conventional one even if they had a size of 20 um. Because all of the electric field applied to the inside of the device was concentrated on trench oxide first and as a result, the breakdown occurred at a high voltage. It is possible that the proposed lateral trench electrode power MOS will be utilized for the smart power IC system.

#### REFERENCE

- [1] B. Jayant Baliga, Proc. of the IEEE, Vol.89, No.6, (2001).

- [2] S.-H. Son, Y.-S. Park, S.-C. Bae, S.-Y. Choi and S.-J Park, J. Korean Phys. Soc. Vol. 40, No. 30 (2002).

- [3] E. G. Kang, S. H. Moon, M. Y. Sung, Microelectronic Journal, Vol.32, No.9, pp 749 (2001).

- [4] E. G. Kang, M. Y. Sung, Trans. on Electrical Electronic Materials, Vol.2, No.3 (2001).

- [5] W. S. Son, S. Y. Choi, Journal of the Korean Physical Society, Vol.44, No.1, pp. 48 (2002)

- [6] E. G. Kang, S. H. Moon, M. Y. Sung, Microelectronics Journal, Vol.32, No.8, 641 (2001)