U09

# in-situ 열처리기법을통한자기터널접합의열적안정성에관한연구

(Role of in-situ annealing process on AlOx insulating barriers in magnetic tunnel junctions )

윤갑수\*, 구자현, 양정엽, 도영호, 김기웅, 김채옥, 홍진표

한양대학교 물리학과

#### Introduction

For the application of magnetic random access memory, magnetic tunnel junctions (MTJs) are being integrated with a complementary metal-oxide-semiconductor technology (CMOS).1 However the CMOS fabrication process typically requires high-temperature process, annealing in a hydrogen atmosphere, plasma etching, insulating layer deposition etc. Therefore it is required to developMTJs with a high thermal stability up to 400 ?.1 However, the requirements for maintaining a high TMR after annealing at temperatures of over 300 oC are still under progress right now. This letter is the first to report a new in-situ annealing process for the enhanced thermal stability in MTJs.

#### Experiments and Results

The MTJs were prepared by utilizing an ultrahigh vacuum dc & rf magnetron sputtering instrument with a base pressure of 10-8 torr. Basic structure of the MTJ device was glass/Ta (100 Å)/Py (100 Å)/IrMn (85 Å)/Co80Fe20 (40 Å)/AlOx (12 Å) /Co80Fe20 (40 Å)/ Py(100 Å)/Ta (200 Å). The insulating layer was typically formed by off-axis remote rf plasma oxidation in a 10 mTorr with mixed gases of oxygen and argon. The in-situ direct radiation annealing (IDRA) process was directly performed on the oxidized insulating barrier for 90 s at different temperatures (  $\sim$  300 ?) without a vacuum break. All ex-situ thermal annealing processes are also done in vacuum (10-4 Torr) for 1h, followed by cooling parallel to the common easy axis of electrode in magnetic field (2 kOe). Finally, we analyzed the dielectric and physical properties on insulating barrier using the surface plasmon resonance spectroscopy (SPRS) techniques.

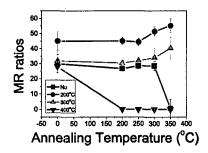

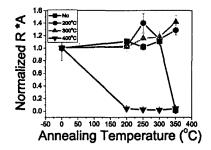

Figure 1(a) and (b) show the annealing temperature (Ta) dependence of TMR and normalized R×A at low bias voltage of 10 mV. The TMR ratio of as-deposited MTJs is increased from 30 % to 45 % of an IDRA temperature of 200?. However, the MTJs which were formed by the IDRA process at 400? showed the electrical breakdown behavior after low temperature ex-situ annealing process. It is due to generation of pin-holes inside the insulating barrier of MTJs when the IDRA process was done at higher temerautre of over 400 oC. As shown in figure 1 (a), the TMR ratio of MTJs is enhanced about 1.3 times up to ex-situ annealing temperature of 350 oC. In addition, the maximum MR ratio of ex-situ annealed samples is observed about 55% after the IDRA process of 200 ?. The TMR of non-IDRA treated MTJs was abruptly decreased to 4 % at above 300 oC. It is expected due to interdiffusion of Mn at the interface of CoFe and IrMn or diffusion of Mn to the oxide barrier. 3-4,6 However, the TMR ratio and the RA product of MTJs formed by the IDRA process of 200 oC or 300 oC were still preserved even at ex-situ annealing temperature of 350 oC. Experimentally observed R×A product of MTJs are comparable to one of TMR ratio of MTJs like on the TMR ratio behavior of MTJs. These results supportthat the IDRA process may have an effect on reconstruction of both Al and oxygen atoms in the insulating barrier of MTJs. Therefore the reconstructed insulating barrier in MTJs enhancesthe thermal stability of MTJs even of ex-situ the annealing temperature up to 350 ?.

Figure 1. Dependence of (a) normalized TMR and (b) resistance area product versus annealing temperature.

## Summary

A new IDRA process was performed to enhance thermal stability of MTJs. After the IDRA process, high TMR radtio of 55 % was obtained at the annealing temperature of 350 ?. The increased TMR ratio of MTJs after IRDA process could be explained by both the enhancement of average barrier height and the reduction of barrier height. Finally, the SPRS results agreed with those of MTJs that were pre-treated by the IDRA process.

### Reference

[1] R. Scheurlein, W. Gallagher, S. S. Parkin, A. Lee, S. Ray, R. Robertazzi and W. Reohr, in proceedings of the 2000 IEEE international Solid-State Circuits Conference, San Francisco, February 2000, Paper TA 7.2.