# Electrical Characteristics of Pentacene-based TFTs with Stacked Gate Dielectrics

Chang-Heon Kang

Dept. of Electrical & Control Engineering, Hong-Ik Univ., 72-1, SangSu-Dong, Mapo-Gu,

Seoul, Korea

Jae-Hoon Park, Yong-Soo Lee, Yeon-Ju Kim and Jong Sun Choi

Dept. of Electrical & Control Engineering, Hong-Ik Univ., 72-1, SangSu-Dong, Mapo-Gu,

Seoul, Korea

## **Abstract**

Using stacked organic gate insulators and active deposited layer of pentacene elevated at temperatures, pentacene-based organic thin-film transistors(OTFTs) improved electrical with characteristics have been fabricated. Stacked PVP(Polyvinylphenol)-polystyrene gate insulators could compensate the demerits and take advantage of the merits of each other [1]. Also, for the better device performance, moderate substrate heating and high deposition rate of pentacene active layer was adopted [2, 3].

1. Introduction

The performance of OTFTs has been considerably improved for several years [4, 5]. Moreover, allorganic TFTs can allow flexible active matrix displays by their integration with organic light emitting diodes or liquid crystal cells on polymeric substrates, and present the possibility for non-planar flexible electronics. Thus, much attention has been recently paid to the all-organic TFT researches [6, 7]. However, OTFTs with organic gate dielectrics prepared using conventional methods only exhibit good performance at high gate voltages and a high dielectric constant gate insulator will reduce the device turn-on voltage. Leakage in deposited organic

dielectrics is another problem, which could be reduced by organic dielectrics with high insulating capability. We have shown that, using stacked organic gate insulators (PVP-polystyrene), the drain current levels of the devices were substantially improved and the more evident saturation aspects and less leakage current values than those of the device with the single PVP gate dielectric layer are ascertained. In this study, for the better electrical characteristics of pentacene-based TFTs with stacked gate dielectrics, the effects of moderate substrate heating on the device characteristics are investigated.

# 2. Experimental Details

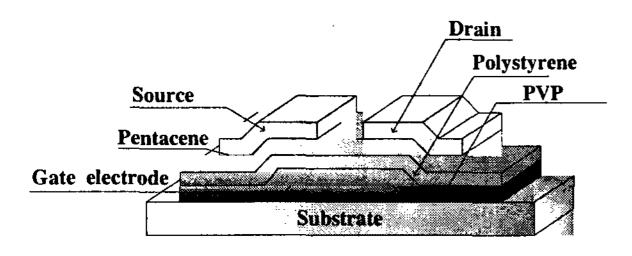

OTFTs with stacked gate insulators was fabricated on glass substrates as shown in figure 1. The channel length and width of the TFTs were 50µm and 5mm, respectively. The device has chromium gate and gold source/drain electrodes, which were formed by evaporations through the shadow masks. PVP and polystyrene were chosen as organic gate dielectric materials. Stacked layer of PVP-polystyrene was spin-coated on the patterned gate electrodes at the speed of 2000rpm. The thickness of the individual PVP and polystyrene layer is 410nm and 250nm, respectively. Ethanol and chloroform were used as the solvents for 5wt% PVP and 1wt% polystyrene solutions.

E-mail address: jschoi@wow.hongik.ac.kr

<sup>&</sup>lt;sup>1</sup> Corresponding author; Tel.: (02) 320-1488 Fax: (02) 320-1110

Pentacene films (65nm thick) were deposited on the dielectric layers under a base pressure of  $10^{-6}$  Torr and at a deposition rate of 2.5Å/sec. During the evaporations, glass substrates were held at  $60^{\circ}$ C to improve molecular ordering in the pentacene layer. The electrical characteristics of the TFTs were measured by Keithley 238 and 617 source-measurement unit. The thicknesses of the layers were measured by ellipsometry (Plasmos, SD-2100) and  $\alpha$ -step profilemeter (Tenkor, 200).

Figure 1. The structure of TFT devices with stacked gate insulators.

#### 3. Results and Discussions

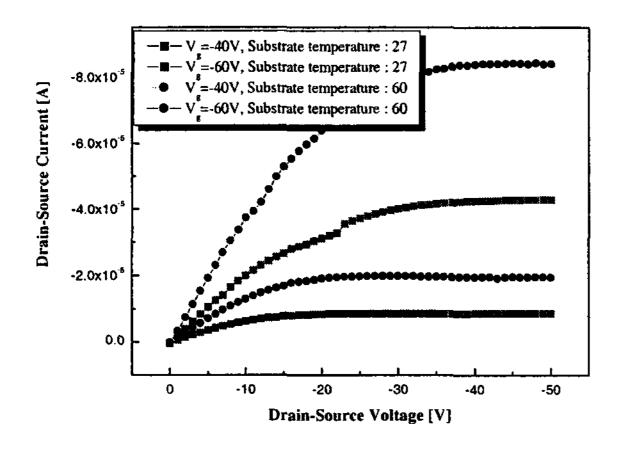

Figure 2 shows the drain current density of the fabricated devices as a function of the drain voltage at the gate voltages of -40, -60V. The saturation current  $(I_{D.sat})$  is increased with the substrate temperature.

Figure 2. The output characteristics with stacked gate insulators.

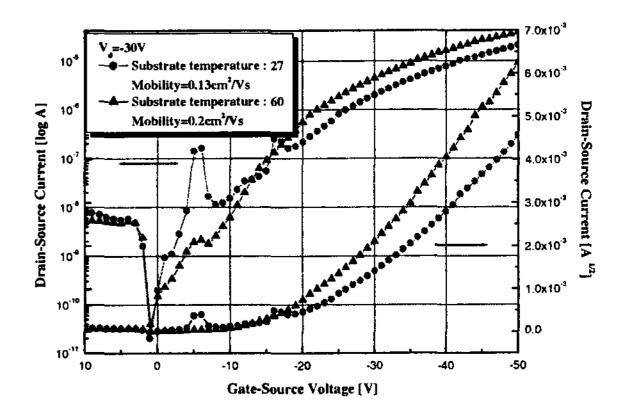

The field effect mobility was extracted for this device from the electrical transfer characteristics in the saturation regime at the drain voltage of -30V, and saturation drain current equation (1):

$$I_{D.sat} = \frac{W\mu_{eff}C_i}{2L}(V_G - V_T)^2 \tag{1}$$

where W is the channel width,  $\mu_{eff}$  is the field-effect mobility,  $C_i$  is the capacitance of the insulating materials per unit area, L is the channel length,  $V_G$  is the gate voltage, and  $V_T$  is the threshold voltage [8]. The field-effect mobility,  $\mu_{eff}$ , of the devices with the moderate substrate heating is improved with 0.13 to  $0.2 \text{cm}^2/\text{Vs}$ . Some critical device parameters were extracted and listed in Table 1.

Figure 2. The transfer characteristics with stacked gate insulators.

Table 1. The device parameters of the devices

| Substrate temperature [°C] | μ <sub>eff</sub><br>[cm²/Vs] | On/off<br>current<br>ratio | Threshold voltage [V] |

|----------------------------|------------------------------|----------------------------|-----------------------|

| 27                         | 0.13                         | $10^{5-6}$                 | -6                    |

| 60                         | 0.2                          | 106                        | -5                    |

#### 4. Summary

Pentacene TFTs with substrate heating and high deposition rate of the pentacene layer have been fabricated. The electrical characteristics of organic TFT were improved with elevated substrate

temperature, which may be attributed to the molecular ordering in the pentacene layer.

## 5. Acknowledgements

This work was supported from Information Display R&D Center, one of the 21<sup>st</sup> Century Frontier R&D Program funded by the Ministry of Science and Technology of Korea.

#### 6. References

- [1] C. H. Kang, J. H. Lee, Y. J. Kim and J. S. Choi: Electrical properties of pentacene TFTs with stacked and surface-treated organic gate dielectrics. SID 03 DIGEST, p 5, 2003.

- [2] J. H. Park, Y. J. Kim, C. H. Kang, Y. S. Lee, and J. S. Choi: Characteristics of pentacene-based thin-film transistors. The 14<sup>th</sup> Molecular Electronics & Devices Symposium, abstract book, p. 45, 2003.

- [3] Y.-Y. Lin, D. J. Gundlach, S. F. Nelson, and T. N. Jackson: Stacked pentacene layer organic thin-

- film transistors with improved characteristics. IEEE ELECTRON DEVICES LETTERS, Vol. 18, No. 12, Dec. 1997.

- [4] G. Gu and S. R. Forrest: Design of flat-panel displays based on organic light-emitting devices. IEEE J. Select. Topics Quantum Electron., vol.4, p. 83-99, Jan./Feb. 1998.

- [5] T. Kawase, H. Sirringhaus, R.H. Friend, T. Shimoda: All-polymer thin film transistors fabricated by high-resolution ink-jet printing. SID 01 DIGEST, p. 40, 2001.

- [6] A. R. Brown, C. P. Jarrett, D. M. de Leeuw, M. Matters: Field-effect transistors made from solution-processed organic semiconductors. Synthetic Metals, p. 37-55, 1997.

- [7] G. Velu and C. Legrand: Low driving voltages and memory effect in organic thin-film transistors with s ferroelectric gate insulator. Applied Physics Letters, p. 659-661, 30 July 2001.

- [8] Donald A. Neamen, Semiconductor Physics & Devices, 2<sup>nd</sup> edition, Irwin, Chicago, p. 457, 1997