# Inspection for Process Improvement during High-Resolution Large-Size LTPS TFT Manufacturing

Jiun-Jye Chang, Chih-Chiang Chen, Ching-Sang Chuang, Yung-Fu Wu and Chai-Yuan Sheu

# Electronics Research and Service Organization/Industrial Technology Research Institute (ERSO/ITRI), Taiwan, ROC

Phone: +886-3-5912330, E-mail: jjchang@itri.org.tw

#### **Abstract**

In order to achieve high-resolution and large-size displays, inspection technology is necessary and important. It is a powerful utility for process and yield improvement for the high valued panel realization. We indicated the challenge of advanced panel manufacturing on inspection ability and throughput. We also investigated the method to judge laser-crystallizing energy by inspection technology. Finally, the total defect number and critical killer defects were classified and discussed in this work.

## 1. Introduction

Low temperature polycrystalline silicon thin film transistor (LTPS TFT) technology has been the most promising method to realize system on panel (SOP) [1]. To achieve high resolution and integrate complex circuit for high-end product, inspection technology is necessary. Therefore, it has been intensively investigated in recent years for fabrication yield improvement and process reliability issues [2,4]. In the flat panel displays manufacturing, the glass substrate becomes more and more large and the fine design rule is also the future trend. In this study, we demonstrate the powerful technology of defect inspection and crystallizing energy judgment method. The inspection technique is an important utility for array yield improvement and high-resolution largesize panel realization. On the other hand, the electrostatic discharge (ESD) was one of the reliability problems in ULSI technology [5] and also the most critical issues in flat panel display [6,7], which lower production yield. The display panel has a multilayered structure combining insulator material and thin film transistors circuits. The thin film transistors typically have worse electrostatic discharge immunity than those fabricated in bulk MOSFET devices, which has a relatively low thermal resistance. As all circuits were integrated in one panel and continuous downscaling of device geometries, the low

temperature polycrystalline silicon TFTs tends to be subject electrostatic discharge during large area glass substrate transfer or TFT-LCD manufacture process.

In this study, we demonstrate the powerful technology of inspection, classification and analysis. We also investigated the method to judge best laser-crystallizing energy for amorphous-silicon film recrystallization process. It is an important utility for TFT array yield improvement and high-resolution panel realization for the future displays.

# 2. Experimental

Top-gate low temperature poly silicon p-channel TFTs array was fabricated in this study. The basic process flow is described as following. First, buffer oxide and 50nm amorphous silicon films were deposited on NEG OA10 glass substrates by PECVD system. After that, 50nm-thick channel film was formed by XeCl excimer laser crystallization and the active area of TFT was patterned after photo process. Subsequently, 100nm gate insulator was deposited by PECVD TEOS oxide. The low resistance molybdenum-tungsten alloy was used for the gate metal. Metal etch was excused by dry etching process. After the source and drain regions impurities doping and activated, the PECVD oxide interlayer was deposited. After contact etching holes source/drain metal patterning, the passivation layer is deposited upon the pixel TFT and storage capacitor. After that, ITO layer is used to be a pixel electrode and contact via to pixel TFT.

A well-design defect inspection machine can detect particles on bare glass and defects on patterned substrate. The advanced functions of a helpful equipment are not only defect inspection but data analysis and sorting. High-speed scan rate, high sensitivity detect-ability and great precisely detecting are the goals to design and setup a defect inspector. High speed and high accuracy are general specifications in the advanced production process.

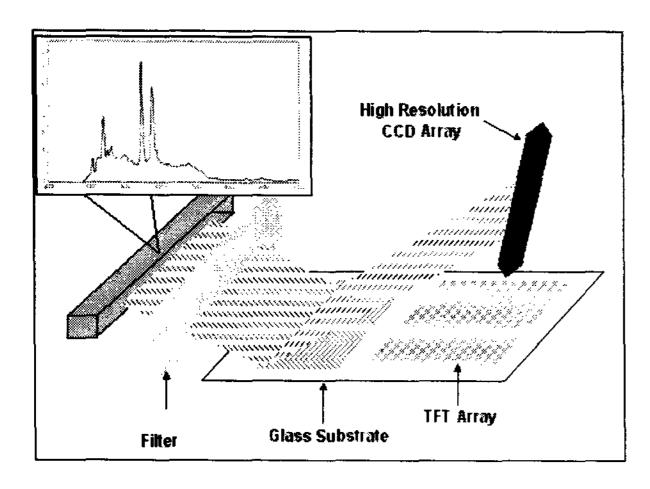

Figure 1 Schematic diagram of inspect technique and methodology.

To achieve the requirement for precisely detecting, stable light source and stage is needed. High-resolution charge-coupling device (CCD) for image capturing and digital data analyzing software are necessary to satisfy high sensitivity detecting. In order to control the process and improve the process reliability immediately, in-line inspection technology is required and must be the future trend.

The schematic diagram of inspection technique for in-line TFT array fabrication is shown in Figure 1. The advanced functions of a helpfully equipment are not only defect inspection but also process improvement. High-speed scan rate, further sensitive and precise detection are the goals to design and setup an inspector. To achieve the requirement for precisely detecting, stable light source and stage is needed. The throughput is dependent on the numbers of charge-coupling device (CCD) and hardware DSP processor performance. We adopt various light sources by filter to judge the best crystallizing energy during laser crystallization process. On the other hand, we also find out the critical defects that affect the panel yield.

# 3. Results and discussions

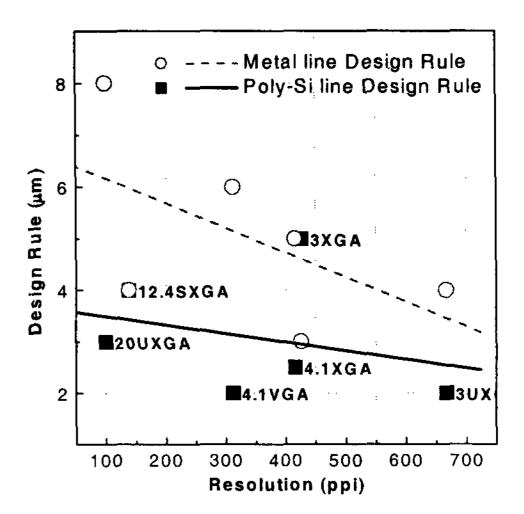

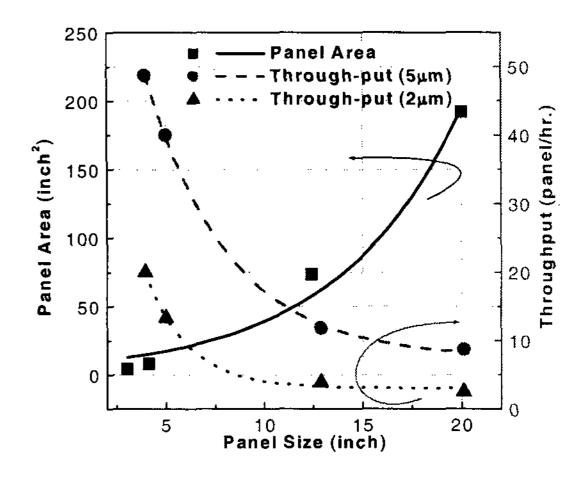

Figure 2 shows the critical design rule of polysilicon lines and metal lines for different resolution products. [8] It is easy to see the higher resolution, the tighter design rule will be. Small design rule made the process hard to be controlled and inspected. In order to inspect the small dimension defect, we have to spend more time than larger defects, as shown in Figure 3. Basically, the larger panels take more time

Figure 2 The approach of critical design rule for ERSO/ITRI different resolution products.

Figure 3 Throughput of defect inspection process with different inspect resolution under various size panel.

to inspect than small ones, especially on high resolution or small size defect inspection.

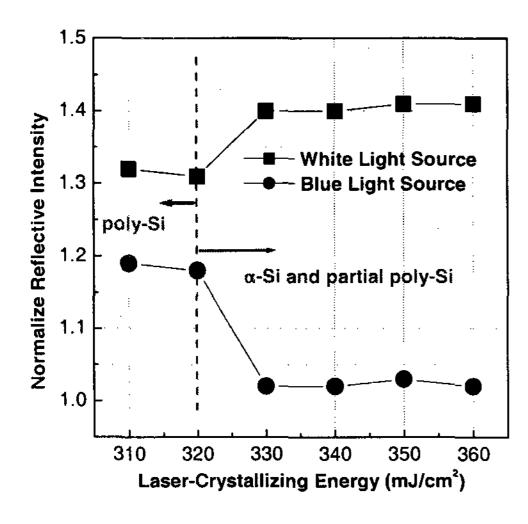

Figure 4 shows the reflective intensity for laser-crystallizing energy judgment by two different light sources. As we know, the best laser energy for crystallization is the most important topic in LTPS TFT process. After inspecting the control sample, the best energy can be judged by the reflective intensity

Figure 4 Reflective intensity inspection for lasercrystallizing energy judgment by two different light sources.

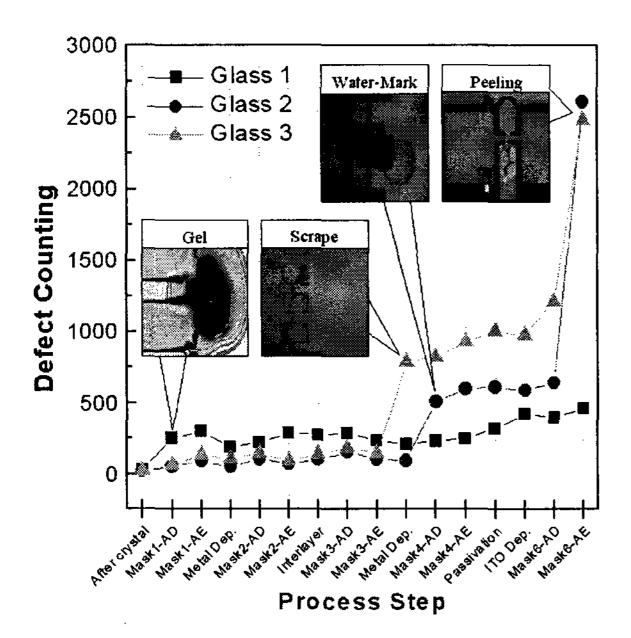

Figure 5 Total defect number counting and critical defect source image capturing during TFT manufacturing.

suddenly changed. Because of the basic material characteristic, different light source for inspection will have different phenomena. This in-line judgment process can be integrated in ELA equipment and

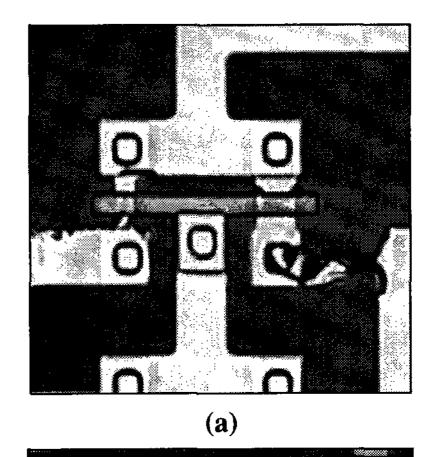

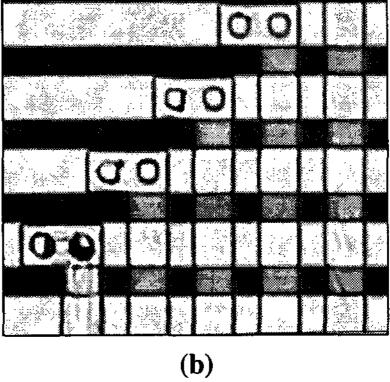

Figure 6 The electrostatic discharge damage on (a) integrated circuits and (b) multi-layer inter-connections of LTPS TFT panel.

suited for roll-to-roll process in the future.

Throughout the whole process, the total defect numbers of each step process were plotted in Figure 5. Some critical defect sources were also indicated and shown after the inspection process. The gel and particle are always the yield killers in TFT manufacture. Scrape issue will happen in the large panel fabricated on large size glass. Watermark is usually found in the un-suit photolithography process. Because of the large area fabrication, film quality and adhesion will become hardly controlled, especially in the final step of TFT process.

The integrated circuit and active matrix array were easily deteriorated by electrostatic discharge and defects occur in panel due to electrostatic breakdown, fusion and burning out, as shown in Figure 6. As design rule shrinks with increasing device integration and circuit complexity, the ESD tolerant margin is narrow. Long metal lines and complex inter-

connections of large area panel make the electrostatic discharge effect seriously. The inspection system can easily detect the damaged defects from ESD issue on periodic routing region, as shown in Figure 6(b). Because of the non-periodic pattern, it is hard to be inspected for whole circuit area. Therefore, by optimizing the environment ionizer and attaching the ESD protection design, we can increase the devices and driver circuit immunity and well control the high-resolution and large-area panels fabrication by inspection system.

## 4. Conclusions

Inspection technology is a powerful technique to improve yield and realize a high-end panel. In this paper, we indicated the challenge of advance panel manufacturing on high resolution and large size panel fabrication. The method to judge best laser-crystallizing energy by inspection technology and critical killer defect sources were also investigated in this work. After well tuning and controlling the processes by inspection system, we can achieve the high-resolution and large-area panels fabrication.

# 5. Acknowledgement

The authors would like to thank the research team members in ERSO for fully support of this work and the financial support of MOEA.

## 6. References

- [1] Norio Tada et al, International Display Workshops, p.1603, (2001)

- [2] Mutsumi Hayashi, Society of Information Display, p.300 (2002)

- [3] M. Hayashi, K. Kitagawa, Display Manufacturing Technology Conference, p.105 (1999).

- [4] K. Nakashima, IEEE Instrumentation and Measurement Technology Conference, p.689 (1994).

- [5] M. D. Ker, IEEE Trans. On Electron Device, 46 p.173 (1999).

- [6] N. Tosic et al., IEEE 38th Annual International Reliability Physics Symposium p.289 (2000).

- [7] S. Uchikoga et al., Digest of Technical Papers of AMLCD 94, p.128 (1994).

- [8] Nien-Hui Kung et. al., Society of Information Display Digest'02, p.908 (2002)