# SILC of Silicon Oxides

C. S. Kang

Dept. of EE, Yuhan College, Kwoian, Sosa, Puchon, Kyunggi, 422-749, The Republic of Korea

#### Abstract

In this paper, the stress induced leakage currents of thin silicon oxides is investigated in the ULSI implementation with nano structure transistors. The stress and transient currents associated with the on and off time of applied voltage were used to measure the distribution of high voltage stress induced traps in thin silicon oxide films. The stress and transient currents were due to the charging and discharging of traps generated by high stress voltage in the silicon oxides. The transient current was caused by the tunnel charging and discharging of the stress generated traps nearby two interfaces. The stress induced leakage current will affect data retention in electrically erasable programmable read only memories. The oxide current for the thickness dependence of stress current, transient current, and stress induced leakage currents has been measured in oxides with thicknesses between 113.4Å and 814Å, which have the gate area 10-3cm2. The stress induced leakage currents will affect data retention and the stress current, transient current is used to estimate to fundamental limitations on oxide thicknesses.

#### 1. Introduction

As the semiconductor industry is growing, integrated metal oxide semiconductor comes to require high immune silicon oxide metal. Silicon oxide film operating important part in switching, insulating and memory. It also requires thin oxide of high quality necessary integration as it is getting more integrated. The stress voltage applied to silicon oxide films generates stress currents, stress induced leakage currents and transient currents. The stress induced leakage current causes destruction of the low voltage in the thin oxide film and the value increases as the thickness of the oxide film decreases. The stress induced leakage current and the transient current are caused by tunneling phenomenon by charging and discharging of the traps generated at the interface. The transient current generated after applying of stress voltage affects the data retention characteristic of the storage cell and the stress current and the transient current increase as the applied voltage increases. The current of oxide film is created by effect due to trapping the tunneling detrapping of the trap induced in the oxide film and the interface. The stress voltage and the trap dependent on polarity cause dielectric breakdown of the cells by inducing negative charge to nearby the negative pole and positive charge to the positive pole. The occurrence of trapping is in proportion to TDDB(Time Dependence Dielectric Breakdown). Such dielectric breakdown of oxide film occurs partially between the positive pole and the negative pole as a high leakage current path is formed by thermal effect. The stress voltage concomitant with reduction of the thin gate oxide film depends on the density of electric charge in the interface according to charge injection. The number of electric charge trapped in the interface of silicon oxide film is indicated in the number of the interface charge after application of stress voltage and the surface potential function. The interface trap density of silicon oxide film during application of high s

A research should be conducted with stress induced leakage currents in order to grasp the diminution of the thin silicon film. The measurement, separation and characteristic of the stress induced leakage current are carried out and appeared by charging and discharging of the traps in oxide films. The currents do not flow all through the oxide film. The stress induced leakage current in the thin oxide film is in proportion to the stress voltage and the stress time. The stress induced leakage current indicates the limitation of scaling down of nonvolatile tunneling oxide film.

In design of thin silicon oxide film, the stress induced leakage currents should be considered. This research is to improve the reliability by studying the leakage current of thin silicon oxide films. This document is a version of the instructions for

## 2. Results and Discuss

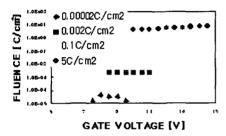

The charge in an oxide film of 113.4Å was measured at each unit of 5C/cm2, 0.1C/cm2, 0.002C/cm2 and 0.00002C/cm2. Figure 1 indicates the relation between the stress voltage and the charge.

Fig. 1. The relationship between fluences and stress voltages.

The currents flowing during application of stress voltage are tunneling currents pass through the layer of the silicon oxide film. These tunneling currents are exponentially in proportion to the stress voltage. The total current capacity in the oxide film is decided by the stress time, which is settled from 1 second to 45,000 seconds. The lowest current capacity is the minimum stress level to measure the variation of quasi stable CV characteristics. The highest value of charge is the value that has no breakdown during the stress voltage. Random breakdowns occurred at 10C/cm2 of charge to high stress voltage.

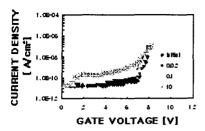

Currents of oxide films are affected by tress voltage. The low level leakage currents increase and the tunneling currents decrease. The low level leakage current is changed by the stress voltage, stress time, stress current capacity, polarity of the stress voltage and sweep rate. Such changes of low level leakage currents are in proportion to the interface trap and the bulk trap created by stress oxide film. Figure 2 shows in the characteristic of the current density of the oxide film to the oxide voltage against the stress charge in a oxide film of 113.4Å.

As the value of the current density to the

voltage after application of stress voltage was compared with the value of the current density to the voltage of the initial oxide film, it was indicated that the low voltage leakage current increased by stress voltage. It was also indicated that the current increased by the stress charge. The tunneling current of the oxide film is induced by the change of the layer type due to the interface trap density and the charge of the oxide film. After application of stress voltage, the separation of the low voltage leakage current was because of the effect of the widen layer due to equal stress induced trapping through the oxide film. The oxide tunneling current depends on the charge equally induced through the oxide film. At the density characteristic of the voltage and current, the variation of the low voltage induced leakage current started when the charge was 0.01C/cm2.

After high stress voltage was induced, the current density of the oxide film to the gate voltage came out in proportion at low level leakage currents, but the increase of current density by high stress voltage was dropped at the point that the gate voltage was 8V. Such effect was due to the trap when the interface charge density of the oxide film became deep by high stress voltage.

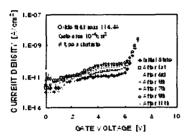

Figure 3 shows the characteristic of the density of the voltage and current which was measured during the repeated weeping from the initial point that stress had not applied in the oxide film of 113.4Å produced in n type silicon.

Figure 3 shows the result of the measurement during normal gate voltage was being applied and that the total capacity of stress current swept at each step was 2.80×10-3C/cm2. It is indicated that, after applying stress to the status of the initial voltage and current, the low level leakage current increased in the characteristic. It is also shown that, as repeated stress increases, the low level leakage current increases. That is, the low level leakage current increased by repeated stress current swept from the initial status.

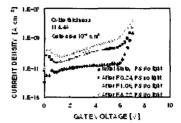

Figure 4 shows the characteristic of the voltage and current to the positive gate voltage after application of stress voltage.

Figure 4 indicates the characteristic of the current and voltage measured while the positive gate voltage was being swept without measuring the light when each current became 0.24, 1.06, 3.22C/cm2 by applying series stress voltage for 100 seconds.

Fig. 2. Current voltage characteristics before and after stress voltage.

Fig. 3. Successive low level current voltage characteristics for repetitive positive gate voltages.

It is indicated that the increase rate of the low level leakage current was very high at the initial stage of stress application and that the increase rate became lower as repeated application of stress was continued. That is, as the stress current capacity increases, the change rate of tunneling on current becomes lower. It is also shown that the change rate of tunneling on voltage is higher at higher capacity of stress current than at lower capacity.

Figure 5 shows the characteristic of the voltage and current to negative gate voltage according to series stress current capacity.

As shown at figure 5, while the gate voltage was being swept in the direction of negative, the light was checked up by generating minority carrier to create tunneling currents. The voltage and current were measured in succession by using negative gate voltage with varying the stress current capacity. The low level leakage current to negative voltage between 2V and 5V increased according to high voltage stress current capacity. The stress capacities were 0.24, 1.05, 3.22C/cm2. The density of the voltage and the current was measured with applying 0.2V step voltage every 2 seconds by using integral time to HP4140B. A similar result on the characteristic of the voltage

current density was given from a test which negative and positive gate voltages were applied to a cell produced in n silicon board. The purpose of researching the light of n board is to form stable electric charge layer by generating minority carrier.

Fig. 4. Current voltage characteristics for positive gate voltages after DC stress.

Fig. 5. Current voltage characteristics for negative gate voltages after DC stress.

Fig. 6. Current voltage characteristics for negative and positive gate voltages after stress fluence 1.06C/cm<sup>2</sup>.

Figure 6 shows the characteristic of the voltage and current measured during application of negative and positive gate voltage after application of stress.

The data of figure 6 represent the density of the voltage and current to negative and positive gate voltage after a sweep stress current, 1.06C/cm<sup>2</sup> was applied at the initial status. The low level

leakage current at 2V ~ 5V of the initial status was  $1.00\times10^{-11}$   $\sim$   $1.60\times10^{-11}$ A/cm<sup>2</sup>, and the current capacity variation to the first positive gate voltage after application of sweep stress currents, 1.06C/cm<sup>2</sup> was  $5.00 \times 10^{-11}$  ~  $2.76 \times 10^{-12}$ A/cm<sup>2</sup> and the current capacity variation to the second gate voltage was 3.00×10-11 1.76×10-12A/cm2. After application of sweep stress currents, 1.06C/cm2, the current capacity variation to the first negative gate voltage was  $4.50\times10-10$  ~  $6.15\times10-10$ A/cm<sup>2</sup> and the current capacity variation to the second negative gate voltage was 2.60×10-11 ~ 1.52×10-12A/cm2. After high stress voltage was applied, when the characteristic of the negative and positive low level voltage and current were measured twice, the second value was lower than the first one in the same form. It is also shown that the decrease of the negative gate voltage and current was greater than that of the positive gate.

Fig. 7. Current voltage characteristics according to the step gate voltage.

Figure 7 shows the characteristic of the voltage and current measured with varying the sweep step voltage.

The sweep voltage was applied as 0.2V, 0.4V, 0.6V, 0.8V, 1.0V to measure the characteristic of the voltage and current. It is indicated that the change rate of the low level leakage current increases as the change rate of the sweep voltage increases.

The low level leakage current against high stress voltage is related to the traps occurred in the oxide film. The increase of the low level leakage current is in proportion to the number of traps occurred by stress in oxide film. Traps are distributed in the entire oxide film and the interface of it. The symmetry of the low level leakage current against the negative and positive

voltage generated by stress indicates that the traps created by the oxide film are distributed in the entire area. The interface trap and the bulk trap are in proportion to the stress current capacity.

## 3. Conclusions

The conclusion from the measurement of stress induced leakage currents by high stress voltage at thin silicon films is as below.

- As the stress voltage increases, the stress induced leakage current increases, and it increases by repeated stress.

- The stress induced leakage current to the negative and positive voltage indicates the same form of characteristic for the voltage and current.

- After application of stress, the low level leakage current decreased when the low level leakage current by repeated stress was measured.

- 4. It is indicated that the increase of the stress induced leakage current by stress voltage was generated by charging and discharging of the traps created in the oxide film.

- 5. It has been found by the measurement of stress and stress induced currents that the variation of traps affects the change of the stress induced leakage currents.

# References

- [1] S. Bruyere, E. Vincent, G. Ghibaudo, Stress Induced Leakage Current in Very Thin Dielectric Layers: Some Limitations to Reliability Extrapolation Modeling, Microelectronics Reliability, Vol. 39, pp. 209~214, 1999

- [2] B. D. Salvo, G. Ghibaudo, G. Pananakakis, B. Guillaumot, G. Reimbold, Study of Stress Induced Leakage Current by Using High Resolution Measurements, Microelectronics Reliability, Vol. 39, pp. 797-802, 1999

- [3] A. S. Spinelli, A. L. Lacaita, D. Minelli, G. Ghidini, Analysis of Space and Energy Distribution of Stress Induced Oxide Traps, Microelectronics Reliability, Vol. 39, pp. 215~219, 1999

- [4] P. Riess, G. Ghibaudo, G. Pananakakis, Analysis of the Stress Induced Leakage Current and Related Trap Distribution, Applied Physics Letters, Vol. 75, No. 24, pp. 3871~3873, 1999