# 삼상 실리콘 기판을 사용한 저가 전극 함몰형 태양전지

권재홍, 이수홍,

\*세종대학교 대학원 전자공학과, \*\*세종대학교 전자공학과

## Buried contact solar cells using tri-crystalline silicon wafer

Kwon, Jea Hong, Lee, Soo Hong, Sejong Univ.

#### Abstract

Tri-crystalline silicon (Tri-Si) wafers have three different orientations and three grain boundaries. In this paper, tri-Si wafers have been used for the fabrication of buried contact solar cells. The optical and micro-structural properties of these cells after texturing in KOH solution have been investigated and compared with those of cast multi-crystalline silicon (multi-Si) wafers. We employed a cost effective fabrication process and achieved buried contact solar cell (BCSC) energy conversion efficiencies up to 15% whereas the cast multi-Si wafer has efficiency around 14%.

**Key words:** Tri-crystalline silicon (Tri-Si); Multi-crystalline silicon (Multi-Si); Buried contact solar cell (BCSC); Anti-reflection (AR) coationg; Solar cell

#### 1. Introduction

Nowadays, fabrication costs of crystalline silicon (c-Si) solar cells is occupied by wafer cost between 55 and 65 % [1-2]. Anyhow, c-Si wafers are by far the dominant absorber materials for today's production of solar cells and modules due to their good price/performance relation and their proven environmental stability. These wafers are mainly produced either by a solar-optimized Czochralski (Cz) growth method yielding c-Si with low defect density or by a directional solidification or a ribbon growth method yielding large grained multi-crystalline (mc-Si) wafers with higher defect density. To further improve the price/performance relation of Cz solar cells, tri-Si is being developed as a high quality wafer material that combines both the high diffusion length of minority carriers of up to 1300 um of c-Si and the productivity of mc-Si. More than 1000 \( \mu \) LID (light induced defect-free) diffusion length could be reached with specially doped tri-crystals. This paper

carried out a systematic investigation on the structural and optical properties of tri-Si wafers with respect to c-Si wafers for solar applications. Tri-Si is a promising candidate for achieving low cost and high efficiency solar cells. Small fraction of grain boundary gives higher lifetime than multi-Si. Due to its high mechanical stability, tri-Si allows both quasi-continuous pulling and thin slicing with higher mechanical yields. Ultra-thin wafer could contribute to the reduction of the amount of silicon consumption and thereby lowering the solar cell cost. Tri-Si is a crystal compound consisting of three mutually tilted mono- crystalline silicon grains. The crystal compound has a (110)-surface orientation in all grains in contrast to the standard (100) orientation of wafers for today's solar cell production. The yield of a 200 µm thick tri-crystalline (110) silicon wafer is almost the same as that of a 300 µm thick standard wafer [3]. BCSC offers the possibility of combining low cost and high performance [4-5]. Part of front

metal contact is buried in a groove, resulting in low shading loss of the metal contact. (110) silicon has been used to increase the optical path length of thin silicon devices by exposing the (111) face by a photolithographic technique at the rear surface [6]. In this work, the processes to make cost effective high efficiency cells were developed using tri-Si wafer. We compared the efficiency performance of cells fabricated on tri-Si with those of multi-Si wafers and single crystalline Cz-wafers. Chemical etching of tri-Si by an anisotropic etching solution was studied. Computer simulation was done using SUNRAY [7] in order to investigate the effect of encapsulation on the performance of textured tri-Si.

## 2. Experimental

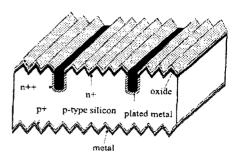

Boron-doped tri-Si, multi-Si and Cz c-Si wafers, each with a thickness of 350 um and resistivity of  $1\sim3$   $\Omega$  cm were used for the fabrication of solar cells. These three kinds of wafers were etched in HF: HNO3 (1:10) to a thickness of 330 µm to remove saw damage. Texturing of tri-Si was conducted in a 30% KOH solution for 30 and 60 mins appropriate isopropyl alcohol (IPA) as surface activation agent. A P2O5 solid source was used for emitter formation and heavy diffusion in the groove. Silicon dioxide was grown by pyrogenic oxidation to mask the top surface during phosphorous heavy diffusion and metal plating into the grooves. Aluminium was evaporated over the rear surface and sintered at 980 °C to provide a back surface field (BSF). Finally, the cells were annealed at 400 °C for 20 mins in forming gas (4 % H<sub>2</sub> in Ar) ambient. A schematic diagram of BCSC is shown in Fig.1.

Computer simulation, using SUNRAY software, was carried out to investigate the effects of V-grooves, composed of (111) faces, on the reflectance of completed solar cells before and after encapsulation. A carrier generation function calculated by SUNRAY was introduced to device simulator PC1D in order to estimate the efficiency enhancement of encapsulated cells.

**Fig.1.** Schematic diagram of BCSC with V-grooved surface [4-5].

## 3. Results and Discussion

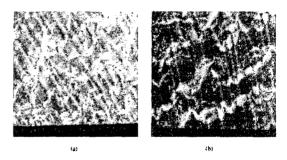

**Fig.2.** shows the SEM (sanning electron microscpe) image of textured surface of tri-Si wafers. The uniform texturing of the surface is found to be an advantage of tri-Si over multi-Si.

Fig.2. SEM images of tri-Si etched in 30% KOH solutions with appropriate IPA at  $70^{\circ}$ C for 30(a) and 60(b) mins.

The etching rate of single crystalline silicon in anisotropic etching solution, such as KOH, decreases in the order of (100) > (110) > (111). For example, the etching ratio of (110) and (111) planes in a mixture of 35 % KOH solution is about 600:1 [8]. The roughness as in Fig.2, therefore, is originated from the difference of etching rate between (110) and (111) planes. After texturing, V-grooves with an angle of  $110^\circ$  are found to appear over the (111) faces, resulting in a facet of  $35^\circ$  [9]. The average pitch of the groove increases with etching time from 7.5  $\mu$ m for 30 mins to 8.6  $\mu$ m for 60 mins. The relationship between (110) orientation and (111) faces and the facet angle are shown in Fig.3.

Fig.3. Orientations of <110> and <111> (a) and facet angle used for simulation using SUNRAY (b).

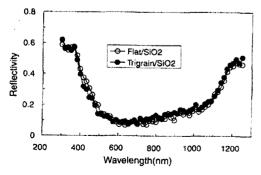

the textured surface, the number reflection depends on the facet angle. Reflected light from (111) face does not bounce from the wafer because the facet angle is less than 45° and the reflectivity of tri-Si wafers, after texturing, cannot be lowered. Fig.4 shows the reflectance of flat and textured tri-Si wafers before encapsulation, as calculated by computer simulation program SUNRAY. In the simulation, the reflectance was calculated for 350 um thick silicon wafers with a 109 nm thick silicon dioxide anti-reflection (AR) coating. As predicted by simple calculation, the reflectance of wafers with a V-groove of facet angle 35° is the same as that of flat wafers. The simulation of optical reflectance with the SUNRAY program tri-Si for the flat and textured after encapsulation is shown in Fig.5.

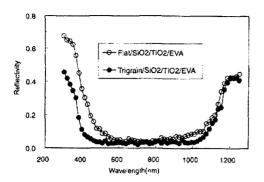

Fig.4. Reflectivities of trigrain wafer textured (●) and flat wafers (○) which were encapsulated after oxidation.

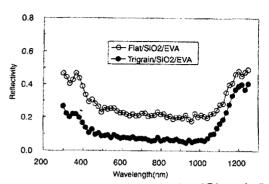

Fig.5. Reflectivities of textured (●) and flat wafers (○) which were encapsulated after oxidation.

The cells are encapsulated under glass by 3 mm thickness of ethylene vinyl acetate (EVA) of refractive index 1.5 (assumed to be same as that of silicon dioxide). Reflection from the front surface of the glass was neglected in the simulation. The reflection of a cell which has a facet angle 35° decreases V-groove of significantly, whereas the reflectance of a flat wafer increases after encapsulation. When the cells are encapsulated, reflected light from the surface of cell is reflected again into the cell at the air/glass interface. Furthermore, encapsulation of textured wafers decreases reflectivity at short and long wavelengths when SiO2/TiO2 was used for the AR layer, as shown in Fig.6. The thicknesses of TiO2 and SiO2 were 43 and 20 nm, respectively, This clearly indicates that the efficiency of solar cells can be enhanced when the textured cells are encapsulated for module fabrication.

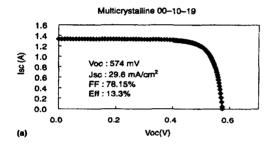

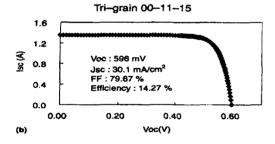

Fig.7 shows the I-V characteristics of cells fabricated on multi-Si and tri-Si wafers. The open-circuit voltage of the cell fabricated using tri-Si was higher than multi-Si wafer due to higher carrier lifetime. Efficiencies of 14.27 and 13.3 % were obtained for tri-Si wafer and multi-Si wafer, respectively.

Fig.6. Reflectivites of textured (●) and flat wafers (○) which were encapsulated after SiO<sub>2</sub>/TiO<sub>2</sub> coating.

Fig.7. Current-voltage characteristics of solar cells made on multi-Si(a) and tri-Si(b) wafer.

| Tuble I. Measured current-voltage parameters for 45 cm² BCSC cells fabricated on multi-Si, Tri-Si and CZ-Si wafe-<br>before encapsulation |                     |                        |        |        |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|--------|--------|--|--|

| Water                                                                                                                                     | V <sub>2</sub> (aV) | J <sub>≠</sub> (mAkm³) | FP (%) | Eq (%  |  |  |

| Maki-Si                                                                                                                                   | 591.0               | 29.9                   | 0-804  | 14-22  |  |  |

| TH-Si                                                                                                                                     | 609-3               | 30-8                   | 0-802  | 15-0   |  |  |

| CZ-Si                                                                                                                                     | 628 - 8             | 30-7                   | 0-809  | 15 - 5 |  |  |

**Table !** shows the output parameters of 45 cm BCSC cells fabricated on multi-Si, tri-Si and Cz c-Si wafers. Efficiencies of 14.22, 15.05 and 15.59 % were obtained for multi-Si, tri-Si and Cz-Si wafers respectively. It was found that the

efficiencies for the three kinds of wafers were mainly determined by the open-circuit voltage. All the wafers were untextured. and short-circuit current densities of the cells are found almost to be the same. The shading loss due to the front metal finger and pad was measured as 10.8 %, which corresponds to a finger with a thickness of 65 µm. The sheet resistance of the heavily diffused layer under the front metal contact was estimates as 5-10  $\Omega/\Omega$ , and that of the emitter as 150-200  $\Omega/\mathbb{I}$ . The relatively low short-current may be attributed to the highly reflective surface of untextured wafers aluminum sintering non-optimized process for the BSF. The efficiency of textured tri-Si wafer was almost the same as that of untextured tri-Si. It seems that the change of open-circuit voltage was caused by the difference in carrier lifetime of each wafer.

| Water   | Oxygen content<br>(ppma) | Carbon contout<br>(ppma) | Effective<br>lifetime (ps) | Effective lifetime<br>after genering (pr |

|---------|--------------------------|--------------------------|----------------------------|------------------------------------------|

| M-Hi-Si | 1-3-1-3                  | 1-43-1-50                | 19-8                       | 29-1                                     |

| Tri-Si  | 13-0-13-6                | 1-11-1-35                | 26-5                       | 41.6                                     |

| CZ-Si   | 16                       | <0.1                     | 62-1                       | 70-2                                     |

**Table II** shows the effective carrier lifetime of multi-Si, tri-Si and Cz c-Si wafers.

Measurement of the effective minority carrier lifetime by microwave-PCD (Photo Conductive Decay) analysis revealed that the lifetime of tri-Si is higher than that of multi-Si wafer, even though tri-Si contains significant oxygen impurity.

Table III. Output parameters of Tri-Si solar cells simulated by PC1D for various surface structures

| Cell structure                  | J <sub>e</sub> (mAicm <sup>2</sup> ) | V <sub>ec</sub> (10√) | 7 <del>7</del> (%) | Efficiency (%) |

|---------------------------------|--------------------------------------|-----------------------|--------------------|----------------|

| Plat/SiO <sub>2</sub>           | 12-34                                | 654-0                 | 79.1               | 16-85          |

| Pas/SiO/EVA                     | 29-1                                 | 651-1                 | 80-0               | 15-16          |

| PaySiO/TiO                      | 34-24                                | 655-5                 | 79-4               | 17-13          |

| Par/SiO/TiO/EVA                 | 34-61                                | 655-8                 | 79-4               | 18-00          |

| Texturing/SiO <sub>2</sub>      | 12-24                                | 653-9                 | 79-6               | 16-79          |

| Texturing/SiO/EVA               | 35-07                                | 656-2                 | 79.4               | 18-26          |

| Texturing/SiO-/TiO <sub>2</sub> | 36-36                                | 657-2                 | 79-2               | 14-93          |

| Texturing/SiO/TiO/EVA           | 36 - 40                              | 657-2                 | 79-2               | 18-95          |

Electron-hole pair generation for each surface structure was calculated by SUNRAY and pot into the PCID for simulation

Table III shows the output performances of cells fabricated on tri-Si wafers. The results were

simulated by PC1D in order to study the effects of encapsulation at several surface conditions. simulation clearly indicates that short-circuit current density of textured cell with SiO<sub>2</sub> AR layer can be enhanced by 2.8 mA/cm after encapsulation. Encapsulation of textured cells is expected to increase the short-circuit current density by about 1.8 mA/cm, even for cells with a SiO<sub>2</sub>/TiO<sub>2</sub> double AR coating. The absolute value of the enhancement depends on the reflectance of glass, because reflection from the front surface of the glass was not included in the simulation indicating that the performance of modules with textured tri-Si wafers is much higher than that of modules with flat wafers, regardless of AR coating layers.

#### 4. Conclusions

Tri-Si, multi-Si and Cz-Si wafers have been used for production of high efficiency solar cell. Efficiencies of 14.22, 15.05 and 15.59 % have been obtained for multi-Si, tri-Si, and Cz-Si wafers, respectively. The solar cells fabricated on tri-Si showed higher open-circuit voltage as compared with cells on multi-Si wafer, due to the longer lifetime. The surface of tri-Si etched in KOH solution showed a V-groove with facet angle 35°. Calculation using PC1D demonstrated that the short-circuit current density of textured cells, with SiO<sub>2</sub> as AR coating layer can be enhanced by 2.7 mA/cm² after encapsulation in EVA.

#### Acknowledgments

This work was supported by nano program of Korean Ministry of Science and Technology.

## References

[1]. T.M. Bruton, G. Luthardt, K.D. Rasch, K. Roy, I.A. Dorrity, B. Garrard, L. Teale, J. Alonso, U. Uglade, K. Declerd, J. Nijs, J. Szlufcik, A. Rauber, W. Wettling, A. Vallera, "A study of the manufacture at 500 MW<sub>p</sub>, p.a. of crystalline silicon photovoltaic modules", Proceedings of the 14th European Photovoltaic Solar Energy Conference,

- Barcelona, pp. 11-16, 1997.

- [2]. J. Palm, A. Lerchenberger, W. Kusian, W. Kruhler, A.L. Endros, G. Mihalik, B. Fickett, J. Nickerson, T. Jester, Processings of the 14th European Photovoltaic Solar Energy Conference, Glasgow, May, pp. 1222–1225, 2001.

- [3]. G. Martinelli, R. Kibizov, "Growth of stable dislocation-free 3-grain silicon ingots for thinner slicing", Applied Physics Letters., Vol.62, pp. 3262-3263, 1993.

- [4]. S.R. Wenham, "Buried contact silicon solar cells", Process in Photovoltaics; Research and Applications, Vol.1, pp. 3-10, 1993.

- [5]. M.A. Green, C. Chong, F. Zang, A. Sproul, J. Zolper, S. Wenham, "20% efficient laser grooved buried contact silicon solar cells" Proceedings of the 20th IEEE Photovoltaic Specialists Conference", Las Vegas, p.411, 1988.

- [6]. J.A. Rand, R.B. Hall, A.M. Barnett, "Back surface texture for optically confining thin silicon films", Proceedings of the 9th European Photovoltaic Solar Energy Conference, Freibug, p.309, 1989.

- [7]. R. Brendel, "Simple prism pyramids: a new light trapping texture for silicon solar cells", Proceedings of the 23rd IEEE Photovoltaic Specialists Conference, Louisville, p.252, 1993.

- [8]. K.E. Bean, "Anisotropic etching of silicon", IEEE Transactions on Electron Devices, No. ED-25, pp. 1185-1193, 1978.

- [9]. E. Bassous, "Fabrication of novel three-dimensional microstructures by the anisotropic etching of (100) and (110) silicon", IEEE Transactions on Electron Devices, No. ED-25, pp. 1178-1185, 1978.