# Calibration Methodology for Transient Enhanced Diffusion of Indium

이준하\*, 이흥주\*, 변기량\*\*, 이주율\*\*,조현찬\*\*\*, 김광선\*\*\*\*

'상명대학교 컴퓨터시스템공학, "중앙대학교 전기전자공학부 "한국기술교육대학교 메카트로닉스공학부, "" 한국기술교육대학교 메카트로닉스공학부,

#### Abstract

We developed a new systematic calibration procedure which was applied to the calibration of the diffusivity, segregation and TED model of the indium impurity. The TED of the indium impurity has been studied using 4 different groups of experimental conditions. Although the indium is susceptible to the TED, the RTA is effective to suppress the TED effect and maintain a steep retrograde profile. Like the boron, the indium shows significant oxidation-enhanced diffusion in silicon and has segregation coefficients at the Si/SiO<sub>2</sub> interface much less than 1. In contrast, however, the segregation coefficient of indium decreases as the temperature increases. The accuracy of the proposed technique is validated by SIMS data with errors less than 5% between simulation and experiment.

### 1. Introduction

Indium, an acceptor dopant in Si, is an alternative of the boron impurity in the channel region for achieving a retrograde channel profile and reduces the SCE (Short Channel Effect) in MOSFETs. This SCE increases the sensitivity of the device electrical behavior to the technological process, via transient effects associated with RTP (Rapid Thermal Processing). Although some results have been published for the behavior of the indium impurity in the inert and oxidizing ambient[1-3], limited data exist for the TED (Transient Enhanced Diffusion) of indium in the RTA(Rapid Thermal Anneal) process[4]. Indium could make a steep channel profile due to its lower diffusivity and strong segregation into the oxide. In this study, the TED phenomena of the indium impurity in silicon are investigated in the range of damage generation from the high energy implantation for the well formation and heavy-dose implantation for the source/drain formation. In addition, the indium profile is systematically calibrated as a newly defined impurity in a process simulator.

#### 2. Experiments and Calibrations

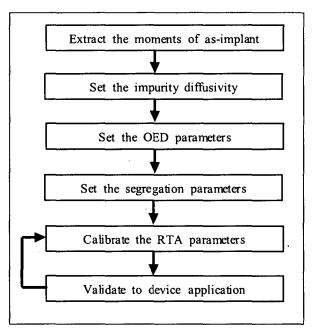

The new systematic calibration procedure of a process simulator for the indium impurity is shown in Fig. 1. Unpatterned <100> oriented p-type silicon wafers were implanted with the

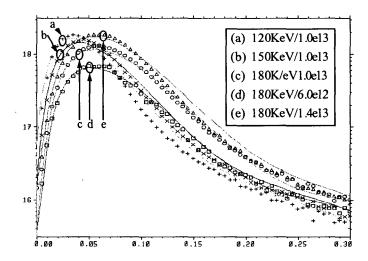

indium impurity. The implant energy was varied between 120KeV and 180KeV. The dose was varied between 6.0E12 and 1.4E13 cm<sup>-2</sup>. First, from the as-implanted indium SIMS profiles, we extracted 9-moments of the dual-Pearson model. The as-implanted calibration results agree well with SIMS data as shown in Fig. 2. Second, the diffusivity parameters and the enhancement factor with segregation parameters during oxidation for the simulation model were taken from the previous results[1-3].

Fig. 1. The process simulator calibration procedure for indium impurity.

Fig. 2. The calibration results of the as-implanted indium impurity compared to SIMS data.

It is assumed that the equations governing the diffusion of indium in silicon are identical to those for the other dopants. These results show that both of indium and boron experience significant oxidation-enhanced diffusion in silicon and has segregation coefficients at the Si/SiO<sub>2</sub> interface much less than 1 at temperatures between 800 and 1050°C. However, the

segregation coefficient of indium decreases as the temperature increases. In order to analyze the TED phenomena of the indium, we performed 4groups of experiments as listed in Table 1.

Table 1. Four groups of experimental conditions to analyze the TED phenomena of indium and boron in silicon.

| Group | RTA | Oxidation | As implant | RTA |

|-------|-----|-----------|------------|-----|

| A     | ×   | 0         | ×          | 0   |

| В     | 0   | 0         | ×          | 0   |

| С     | 0   | 0         | 0          | 0   |

| D     | ×   | 0         | 0          | 0   |

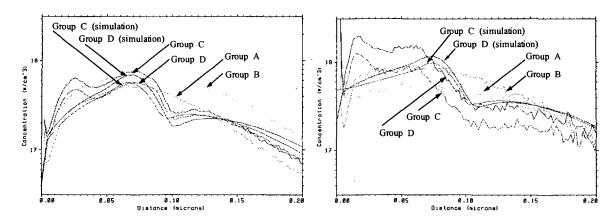

The boron impurity was also experimented under the same conditions for comparison. The purpose of these conditions is to extract the damage effect of the phosphorus high-energy implantation for the well formation and the arsenic heavy-dose implantation for the source/drain formation. The experiment was carried out as follows. Starting from the asimplanted wafers, the first RTA is performed prior to the oxidation on B and C groups only. Then, dry oxidation (850°C/30min.) and inert annealing (900°C/20min.) are applied to all wafers. To monitor how the TED affects the channel impurity redistribution, the damage generation is made on C and D groups by high dose (5.0E15 cm<sup>-2</sup>) arsenic implantation which is the condition for the source/drain process. Finally, the second RTA (1000°C/30sec) is processed. The SIMS data were obtained after removing the oxide layer. The TED calibrations are done with process simulator using a fully coupled model for dopant diffusion and a scaled "+1" model to account for point defects created by the implant damage[5]. The scaled damage factor is approximately 1-1.2 interstitials per implanted ion for phosphorus and 2-2.3 for arsenic. The simulation profiles for the final indium dopant show good agreement with the SIMS profiles as shown in Fig. 3. The SIMS profiles of Fig. 3 and Fig. 4 have the first peak at 200Å depth. However, the SIMS data seem to be not correct in this region so that we do not perform the calibration. Compared to the boron TED as shown in Fig. 4, the indium has the lower peak concentration and the surface concentration is much lower than the boron.

Fig. 3. The comparison of simulation results to SIMS data for the indium TED effects.

Fig. 4. The comparison of simulation results to SIMS data of the boron TED effects.

## 3. CONCLUSIONS

We developed a new systematic calibration procedure which was applied to the calibration of the diffusivity and TED model of the indium impurity. The TED of the indium impurity has been studied using 4 different groups of experimental conditions. Although the indium is susceptible to the TED, the RTA is effective to suppress the TED and maintain a steep retrograde. With this calibration tool, we can optimize and integrate the process conditions for developing high performance devices scaled down to the  $0.1-\mu m$  region by suppressing the RSCE and increasing the driving capability of a device.

## **REFERENCES**

- [1] G. G. Shahidi, Bijan Davari, Thomas J. Bucelot, et. al., "Indium Channel Implant for Improved Short-Channel Behavior of Submicrometer NMOSFET's," IEEE ED Letters, Vol. 14, No. 8, pp. 409-411, Aug. 1993.

- [2] M. Takase, K. Yamashita, and B. Mizuno, "Study of Indium Doping Effect on High Performance Sub-Quarter Micron NMOS: Vt Control and Poket Implantation," SSDM, pp.510-511, 1997.

- [3] L. C. Kizilyalli, T. L. Rich., F. A. Stevie, and C. S. Rafferty, "Diffusion parameters of indium for silicon process modeling," J. Appl. Phys. 80(9), pp. 4944-4947, Nov. 1996.

- [4] M. Cao, P. Griffin, P. Vande Voorde, C. Diaz and W. Greene, "Transient-Enhanced Diffusion of Indium and its Effects on Electrical Characteristics of Deep Sub-Micron nMOSFETs," Symp. on VLSI Technology, pp. 85-86, 1997.

- [5] Seong-Dong Kim, Cheol-Min Park and Jason C. S. Woo "Advanced Model and Analysis of Series Resistance for CMOS Scaling Into Nanometer Regime," IEEE-ED, Vol. 49, No. 3, pp457-466, March 2002.