# Space Vector Modulated Three-Phase Soft-Switching Active Rectifier and Its Performance Evaluations

Yuma Fujii, Tarek Ahmed, Kosuke Imamura, Eiji Hiraki, and Mutsuo Nakaoka,

Department of Electrical and Electronics Engineering

Yamaguchi University

Yamaguchi, Japan

**Abstract**: This paper presents an instantaneous space vector modulated voltage source type three-phase soft-switching PFC rectifier using a single auxiliary resonant DC Link snubber for alternative energy utilizations.

In the first place, the operating principle of an active auxiliary resonant DC link snubber circuit is described including its unique features. In the next place, the simulation analysis of three-phase soft-switching PWM rectifier is implemented, and the operating performances of the three-phase voltage-fed PWM rectifier treated here, which can operate under the conditions of sinewave line current shaping and utility power factor are evaluated and discussed on the basis of this simulation results.

**Index Terms**: Soft-switching, Active auxiliary resonant DC link snubber, Three-phase PFC rectifier, Instantaneous space vector modulation, Instantaneous power control

#### 1. INTRODUCTION

In recent years, the latest developments of the high-frequency switching sinewave PWM mode high performance inverters and active rectifiers based on soft-switching PWM power conversion conditioning circuits technologies have attracted special interest for CVCF/VVVF high-power applications in industrial power utilization and telecommunication energy systems as well as distributed power supply systems. The main objectives on research and development of new soft-switching circuits and related control schemes are to minimize the switching power losses of power semiconductor devices in high-frequency pulse modulated power conditioners as well as to reduce the electrical dynamic voltage and current stresses, dv/dt and di/dt related EMI/RFI noises and high-frequency leak current.

The soft-switching power conversion circuit topology is divided into three categories; auxiliary resonant DC link snubber type, auxiliary AC link snubber and auxiliary resonant commutation bridge leg link snubber. Of three, the three-phase soft-switching PWM rectifier with a simple auxiliary resonant DC link snubber is more suitable for relatively small power applications

In this paper, the new conceptual circuit configuration of digitally-controlled three-phase voltage source soft-switching PWM-PFC rectifier topology with a single Auxiliary Active Resonant DC Link (ARDCL) snubber, which can operate under a condition of Zero Voltage Soft-Switching (ZVS) on the three-phase bridge arm switches of the rectifier, is proposed and its operating principle is described under ideal operating condition. In addition, the operating performances of the three-phase ARDCL snubber-assisted soft-switching PFC rectifier treated here is evaluated and discussed on the basis of

simulation results.

# 2. NEW THREE-PHASE SOFT-SWITCHING PFC RECTIFIER

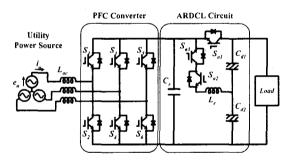

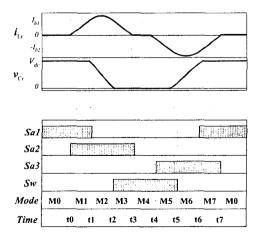

Fig.1 shows a schematic diagram of three-phase voltage source soft-switching PFC rectifier topology with a simple ARDCL snubber circuit. The proposed ARDCL snubber circuit is connected to the DC busline of the three-phase bridge rectifier output side which is composed of the quasi-resonant capacitor  $C_r$  in the DC busline, the DC capacitors  $C_{dl}/C_{d2}$  for the divided voltage source, the active power switch  $Q_{ul}$  for DC output voltage clamping, and the bi-directional active power switches,  $Q_{u2}$ ,  $Q_{u3}$  in series with quasi resonant inductor  $L_r$ . To achieve complete ZVS operation, the ARDCL snubber circuit acts as the soft-switching commutation scheme of three-phase voltage source PFC rectifier. In Fig.2, typical voltage and current waveforms of ARDCL circuit are depicted to explain their

Fig. 1. Auxiliary active resonant DC link three-phase PFC converter

Fig. 2. Operating waveforms and switching gate pulse sequences

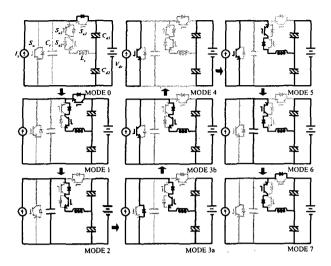

Fig. 3. Mode transition of Auxiliary Resonant DC link Circuit

basic operation principle. In this case, there are 9 operation modes as depicted in Fig.3. The operating principle of the ARDCL snubber circuit is described as follows;

[Mode 0];  $(t < t_0)$

The load current  $I_1$  is flowing through  $D_{al}$ , and resonant capacitor voltage  $v_{cr}$  is charged up to  $V_{s}$ . [Mode 1];  $(t_0 - t_1)$

$S_{a2}$  is turned on under a condition of soft-switching zero

current switching (ZCS). The resonant inductor current  $i_{Lr}$ through  $D_{a3}$  and  $S_{a2}$  begins to increase linearly. When the resonant inductor current  $i_{Lr}$  reaches the specified value  $I_{bl}$ ,  $S_{al}$  is turned off under a principle of ZVS commutation. [Mode 2];  $(t_1 - t_2)$

After turning off  $S_{al}$  with ZVS, the resonant capacitor  $C_r$ begins to discharge. This is based on a quasi-resonance owing to the resonant inductor  $L_r$  and the capacitors  $C_r$ . [Mode 3];  $(t_2 - t_3)$

At time  $t_3$ , as soon as the resonant capacitor voltage  $v_{cr}$ reaches zero,  $S_w$  begins to conduct and  $i_{Lr}$  starts to decrease linearly, and when  $i_{Lr}$  decrease to zero, this mode changes to the next mode; mode 4.

[Mode 4];  $(t_3 - t_4)$

In mode 4,  $i_{Lr}$  remains zero, and resonant capacitor voltage  $v_{cr}$  is also kept zero. This mode is defined as "zero voltage holding mode".

[Mode 5];  $(t_4 - t_5)$

At  $t_4$ , when  $S_{a\beta}$  is turned on under a principle of ZCS,  $i_{Lr}$ begins to increase linearly towards minus direction and continues to rise until another specified value  $-I_{h2}$ .

[Mode 6];  $(t_5 - t_6)$

After turning off main switch  $S_w$  with ZVS, the resonant capacitor voltage  $v_{cr}$  begins to charge up to  $V_{s}$ .

[Mode 7];  $(t_6 - t_0)$

At time  $t_6$ , as soon as  $v_{cr}$  reaches  $V_x$ ,  $D_{al}$  begins to conduct and  $i_{Lr}$  begins to decrease linearly towards minus direction. When the resonant inductor current  $i_{Lr}$  becomes zero,  $S_{u3}$  is turned off with ZCS, and the mode moves to mode 0.

## 3. DIGITAL CONTROL IMPLEMENTATION FOR THREE-PHASE PWM RECTIFIER

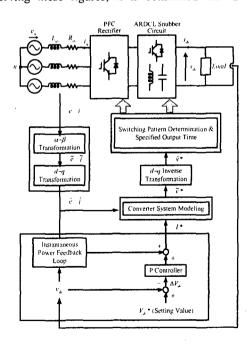

The main power circuit of three-phase voltage source soft-switching PFC rectifier using a single ARDCL circuit is shown in Fig.1. Its control system is schematically described in Fig.4.

This control system is based on a digital control strategy on the d-q coordinate frame under the time-sharing allocated space voltage vector based-upon synchronous rotating d-q coordinate modulation scheme, using this control scheme transformation frame in three phase power processing system, real time control processing will make simple under conventional modern control theory because the feedback control variable becomes only one DC value.

#### 4. SYSTEM EVALUATIONS AND DISCUSSIONS

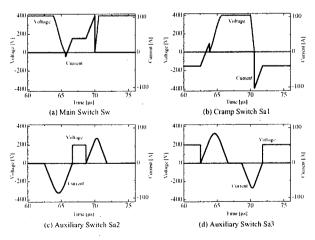

In this case, the maximum output power of the three-phase voltage source type soft-switching PFC rectifier treated here is designed for the rated power 10kW. Fig.5 (a) shows the simulated voltage and current waveforms at soft-switching turn on and turn off for the main switch in the three-phase PFC rectifier. Taking a look at turn on waveforms at turn on switching, the overlap and current waveforms under voltage between soft-switching condition is considered to be zero. This indicates that the switching losses of this soft-switching rectifier can be remarkably reduced. Furthermore, significant reduction for dv/dt and di/dt values of the power switches in three-phase soft-switching PFC rectifier main switches suggests that EMI/RFI noises could be reduced. Fig.5 (b)-(d) illustrates the simulated voltage and current waveforms of the auxiliary power semiconductor switching devices  $(S_{a1}, S_{a2} \text{ and } S_{a3})$  in ARDCL.

Observing these figures, it is confirmed that ZVS/ZCS

Fig. 4. Schematic control system of three-phase PFC converter

commutation turn on and ZVS commutation at turn off operations for  $S_{al}$ , ZVS/ZCS turn on and ZCS turn off operations for  $S_{a2}$ , ZVS/ZCS turn on and ZVS turn off operations for  $S_{a3}$  can be achieved in the mentioned power switches.

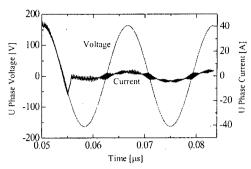

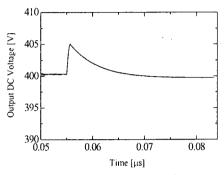

It is proved that the output voltage is regulated to a constant value of 400V in a DC voltage feedback loop. Transient response of the proposed three-phase voltage source soft-switching PFC rectifier is illustrated in Fig.6 when the load resistance is abruptly changed from  $16\Omega$  to  $160\Omega$ . Fig.7 shows the input sinewave current shaping under the rated output power. From Fig.6 and Fig.7, the output voltage is continuously regulated to a constant value with the control implementation of the instantaneous power feedback algorithm and DC regulation loops under soft-switching PFC rectifier operation.

### REFERENCES

- Takaharu Takeshita: "Control Schemes of Voltage and Current Source PWM AC/DC Converters", Proceedings of Japan Society of Power Electronics Seminar Textbook, Nov. 1996.

- [2] Tadahito Aoki, Yousuke Nozaki, and Yutaka Kuwata: "A Zero-Voltage Switching PWM Inverter Using a Quasi-Resonant DC Link Circuit", Trans. on IEICE, B-1 Vol. J80-B-1 pp. 848-855 Nov. 1997.

Table 1. Design Specifications and Circuit Parameters

| Symbol         | Parameter                      | Value           |

|----------------|--------------------------------|-----------------|

| E              | 3-Phase AC Source Voltage      | 200.0 [V]       |

| $f_{\epsilon}$ | Utility AC Frequency           | 60.0 [Hz]       |

| $V_{di}$       | DC Output Voltage              | 400.0 [V]       |

| $P^{"}$        | Rectifier Output Power         | 10.0 [kW]       |

| $L_{\ell}$     | AC Filter Inductor             | 1.0 [mH]        |

| $C_{dx}$       | DC Voltage Smoothing Capacitor | 5000.0 [μF]     |

| $L_r$          | Auxiliary Resonant Inductor    | 3.98 [µH]       |

| $C_r$          | Auxiliary Resonant Capacitor   | 0.159 [μF]      |

| $R_{land}$     | Load Resistance                | $16.0 [\Omega]$ |

| f <sub>s</sub> | Switching Frequency            | 20.0 [kHz]      |

Fig. 5. Voltage and current waveforms of the power switches in three-phase soft-switching PFC rectifier

Fig. 6. Output voltage waveform when the load parameter is changed

Fig. 7. Input voltage and current waveforms when the load parameter is changed