# A New Pixel Structure with Vth Variation Compensation Scheme for Poly-Si TFT AMOELD

Yang Wan Kim, Sung-Ryong Lee and Oh-Kyong Kwon

Division of Electrical and Computer Engineering, Hanyang University, Seoul, Korea, +82-2-2290-0359, okwon7@chollian.net

Keum-nam Kim, Yong-Sung Park, Sun-A Yang, Dong-Young Shin, Byung-Hee Kim and Ho-Kyoon Chung

R&D Center, Samsung SDI Co., LTD, suwon, Kyonggi do, Korea

#### **Abstract**

We have proposed new pixel structures for Active Matrix OELD (AMOELD) to improve the uniformity of luminance and manufactured a full-color 3.6-inch QVGA AMOELD. The proposed pixel structures, composed of four TFTs and one capacitor, can display 64 gray scales by compensating threshold voltage (Vth) variation of driving TFTs. Non-uniformity and peak intensity of measured luminance are under 14% and over 200cd/m², respectively.

#### 1. Introduction

Because organic electro-luminescent display (OELD) has advantages such as simple structure, emissive type, fast response time and wide viewing angle, it has been studied widely for an application in high efficiency displays. There are two kinds of addressing methods for OELD. One is passive-matrix addressing method and the other is active-matrix addressing method. The passive-matrix OELDs (PMOELDs) have strict limitations on the luminance and the resolution. Therefore, active-matrix **OELDs** (AMOELDs) are presently considered to be the most appropriate choice for large size and high resolution displays. AMOELDs demonstrated their potential for higher image quality [1]. However, non-uniformity of gray-scale is critical issue for AMOELDs. In realizing high gray-scale, there were several suggestions such as digital driving methods using two thin film transistors (TFTs) [2, 3], voltage programmable pixel structures [4, 5] and current programmable pixel structures [6].

We have proposed new voltage programmable pixel structures, composed of four TFTs and one capacitor, and manufactured a 3.6-inch QVGA AMOELD with 64 gray-scale.

## 2. Voltage Programmable Pixel Structures

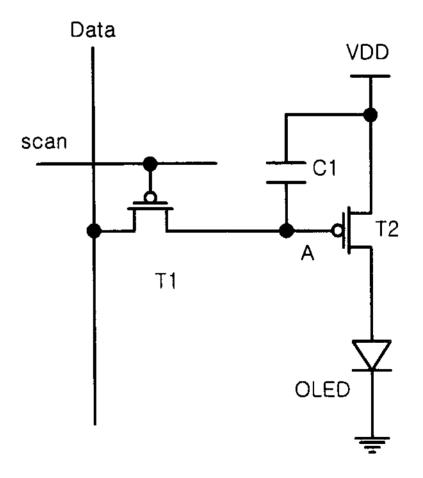

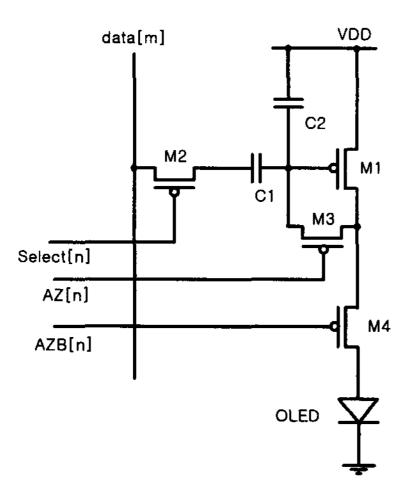

The conventional pixel structure, composed of two TFTs and one capacitor, is shown in figure 1. T1 is pixel switch TFT, which samples data voltage. T2 is driving TFT, which supplies the constant current to organic light-emitting diode (OLED) for a frame time. C1 is storage capacitor, which is storing the gatesource voltage of T2 for a frame time. Although this structure is simple and has high aperture ratio, pixelto-pixel luminance non-uniformity, due to the threshold voltage variation of T2, could be a problem for mass production. To solve above pixel-to-pixel luminance non-uniformity problem, R. Dawson et. al proposed the pixel structure which compensates the threshold voltage variation of the driving TFT. The pixel structure proposed by R. Dawson et. al is shown in figure 2. Although this structure may be a good candidate for large size display, it has some problems such as complexity of the driver circuits and low aperture ratio due to independent three control signal lines.

Figure 1. The conventional pixel circuit composed of two TFTs and one capacitor.

Figure 2. The pixel structure proposed by R. Dawson et. al.

# 3. Proposed Pixel Structure

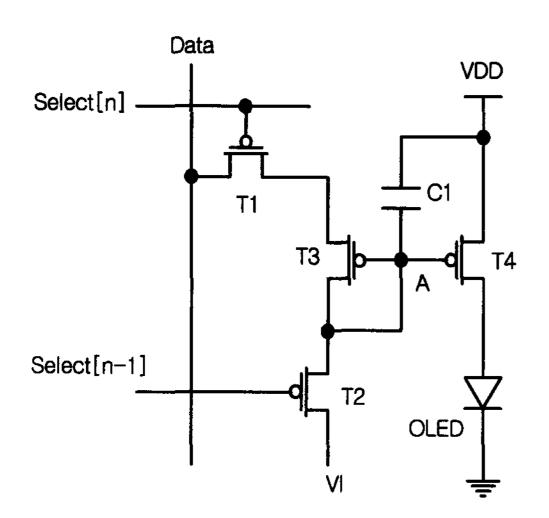

To overcome the problems in voltage programmable pixel structures such as pixel-to-pixel non-uniformity, complexity of driver circuits and low aperture ratio, we have proposed new pixel structures. The proposed pixel structure is shown in figure 3. This structure consists of four TFTs and one storage capacitor. T1 is pixel switch TFT and T4 is driving TFT. Additional diode connected TFT, T3 is used for detection of the threshold voltage of the driving TFT, T4. T2 is used to initialize the stored voltage at the capacitor, C1. This structure can compensate the threshold voltage variation of driving TFT, T4 with simple driver circuits and relatively high aperture ratio.

Figure 3. The proposed pixel structure I

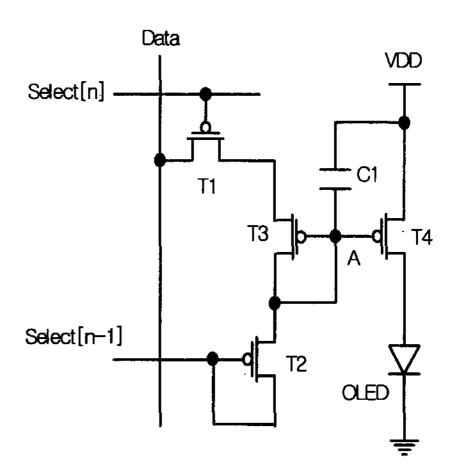

Figure 4. The proposed pixel structure II.

Figure 4 is another configuration of the proposed pixel structure. The gate and source node of T2 is connected together so that VI line can be removed and higher aperture ratio can be obtained.

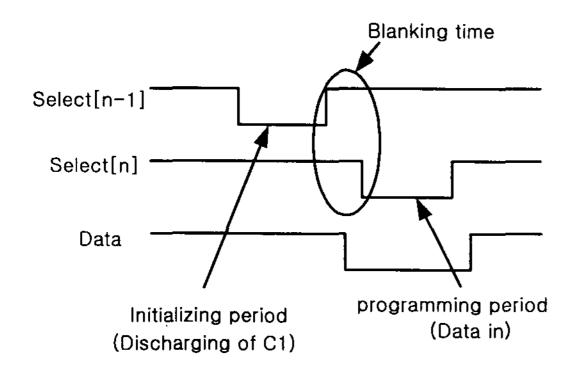

The timing diagram of the proposed pixel structures is shown in figure 5. Input data voltage is applied by enabling select line (Select[n]). At this time, if the voltage of point A is higher than the input data voltage, that is diode connected TFT, T3 is reverse-biased, the data voltage cannot be programmed correctly. Therefore the T3 should be forward-biased and the initialization of making the voltage of storage capacitor lower than that of input data is necessary. The operation of this circuit can be described as follows:

Initializing period: previous select line (Select[n-1]) is selected and the storage capacitance C1 is discharged by initial voltage, VI.

Programming period: select line (Select[n]) is selected and data voltage is applied. Here the threshold voltage variation of driving TFT, T2 is compensated by diode connected TFT, T3. If the threshold voltage of T3 and T4 are same, each threshold voltage is canceled. So it is possible to control OELD current independent of driving TFT's threshold voltage, as shown in equation (1).

$$I_{OLED} = \frac{\beta_p}{2} \left( |V_{GS_4}| - |V_{th_4}| \right)^2 = \frac{\beta_p}{2} \left( |VDD - (V_{DATA} - |V_{th_3}|) - |V_{th_4}| \right)^2$$

$$= \frac{\beta_p}{2} \left( |VDD - V_{DATA}| \right)^2$$

(1)

where the  $V_{GS\_4}$  is voltage difference between the gate node and source node of the driving TFT, T4,  $V_{th}$  3

Figure 5. Timing diagram of the proposed pixel structures.

and  $V_{th\_4}$  are the threshold voltage of T3 and T4, respectively, and  $V_{DATA}$  is the input data voltage.

In the timing diagram, because input data voltage should be changed between initializing period and programming period, blanking time is necessary.

## 4. Panel Design

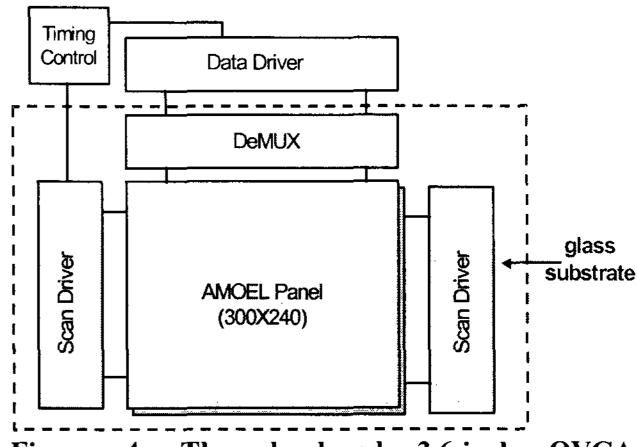

The block diagram of the developed 3.6-inch QVGA AMOELD panel is shown in figure 4. The pixel arrays, the scan driver circuits and the demultiplexing (DeMUX) circuits are integrated on a same glass substrate. Conventional TFT-LCD data driver LSI is used for data driving LSI.

The pixel size, which pixel composed of R, G, B pixels, is  $240(H) \times 240(V) \mu m^2$ . To improve aperture ratio, the storage capacitor is formed by overlapping of gate metal, wiring metal and ITO. In R, G and B pixels, each driving TFT size is designed by adapting maximum current ratio of each pixel. To obtain white balance, emitting ratio of R, G, B cell is 3:6:1 and maximum current is matched by emitting ratio. As the result the aperture ratio of 33.8% is obtained.

The scan drivers, which consist of shift register, level shifter and buffers, are placed on both sides of the panel.

The DeMUX circuits are placed on upper side of the panel for reducing the number of data driver LSIs. The DeMUX circuit consists of DeMUX switches, level shifter and buffers, which drive gate of DeMUX switches. Using 1-to-3 DeMUX switches 900 data lines can be driven by only a 300channel data driver LSI.

Figure 4. The developed 3.6-inch QVGA AMOELD panel diagram.

# 5. Measured Results

To evaluate the non-uniformity of panel, we measured luminance at difference points on a panel. As the results The R, G, B average luminance is 42.9cd/m<sup>2</sup>, 91.5cd/m<sup>2</sup>, 32.9cd/m<sup>2</sup> respectively and the luminance with full white image is about 200cd/m<sup>2</sup>. The non-uniformity of measured luminance with full white image is less than 14%.

The specifications and characteristics of fabricated 3.6-inch AMOELD are summarized in table 1. The 3.6-inch display has 300×240 pixels, each of which has individual R, G, B pixel. Aperture ratio of the pixel is about 33.8%. R, G, B pixel yields CIE coordinates of (0.61, 0.35), (0.31, 0.59), (0.16, 0.12) respectively.

Figure 5 shows an example of the displayed image of fabricated AMOELD. As expected, large viewing angle and video rate compatible fast switching response are obtained.

### 6. Conclusions

Novel pixel structures, compensating the threshold voltage variation of driving TFTs, have been proposed and fabricated for 3.6-inch low-temperature polysilicon AMOELD. 64 gray-scale and less than 14% pixel-to-pixel non-uniformity can be achieved with proposed pixel structure which has 33.8% aperture ratio. The fabricated AMOELD panel has many excellent features such as good pixel-to-pixel luminance uniformity, high moving picture quality, good gray-scale expression.

Figure 5. The displayed image of fabricated 3.6-inch AMOELD

Table 1. The characteristics of fabricated 3.6-inch AMOELD

| Parameter             | Features                         |

|-----------------------|----------------------------------|

| Display size          | 3.6 inch                         |

| Resolution            | QVGA                             |

| Pixel Number          | 300× RGB × 240                   |

| Pixel pitch           | $240 \times 240 \ \mu\text{m}^2$ |

| Aperture ratio        | 33.8 %                           |

| Peak Luminescence     | $> 200 \text{ cd/m}^2$           |

| Gray scale            | 64 gray                          |

| CIE Color Coordinates | R (0.61, 0.35)                   |

|                       | G (0.31, 0.59)                   |

|                       | B (0.16, 0.12)                   |

| Driving Voltage       | 11V                              |

| Emission type         | Bottom emission                  |

#### 7. References

- [1] T. Sasaoka, M. Sekiya, A. Yumoto, J. Yamada, T. Hirano, Y. Iwase, T. Yamada, T. Ishibashi, T. Mori, M. Asno, S. Tamura and T. Urabe, SID '01 Digest, p. 384 (2001)

- [2] M. Mizukami, K. Inukai, H. Yamagata, T. Konuma, T. Nishi, J. Koyama, S. Yamazaki and T. Tsutsui, SID '00 Digest, p. 912 (2000)

- [3] K. Inukai, H. Kimura, M. Mizukami, J. Maruyama, S. Murakami, J. Koyama, T. Konuma and S. Yamazaki, SID '00 Digest, p. 924 (2000)

- [4] R. Dawson, Z. Shen, D.A. Furst, S. Connor, J. Hsu, M.G. Kane, R.G. stewart, A. Ipri, C.N. King, P.J. Green, R.T. Flegal, S. Pearson, W.A. Barrow, E. Dickey, K. Ping, C.W. Tang, S. Vanslyke, F. Chen, J. Shi, J.C. Sturm and M.H. Lu, SID '98 Digest, p. 11 (1998)

- [5] R. Dawson, Z. Shen, D.A. Furst, S. Connor, J. Hsu, M.G. Kane, R.G. stewart, A. Ipri, C.N. King, P.J. Green, R.T. Flegal, S. Pearson, W.A. Barrow, E. Dickey, K. Ping, S. Robinson, C.W. Tang, S. Vanslyke, F. Chen, J. Shi, J.C. Sturm and M.H. Lu, IEDM '98, p. 875 (1998)

- [6] A. Yumoto, M. Asano, H. Hasegawa and M. Sokiya, IDW '01, p. 1395 (2001)