## Recent Trend of Low Temperature Poly Silicon Technologies in TFT-LCD

# C.W.KIM, H.J.Kim, H.G.LEE, H.G.MIN, J.W.HWANG, S.W.CHO, C.K.RYU, C.LEE, M.K.KANG, K.H.CHUNG

## R&D Team, AMLCD Division, Samsung Electronics, Kiheung, Korea

## **ABSTRACT**

Recent trends of low-temperature polycrystalline Si (LTPS) TFT technologies are presented. Characteristics of LTPS TFT processes are compared with those of a-Si TFT's. In order to compete with well-established a-Si TFT-LCD technology, LTPS process has to be as simple as possible. One of the most critical processes, recrystallization of a-Si thin films, could be the process for the differentiation of LTPS technology. Along with these technical reviews, a recent development of the 5.0-inch LTPS TFT-LCD is presented. In order to achieve high-performance display characteristics and save the power consumption, the transflective mode is adopted. The 5.0-inch display with 186 pixel-per-inch, high-resolution LCD was measured to be 10% for the reflectance and 70:1 for the contrast ratio. This display is designed for a high information content handheld PC (HHPC) application.

#### Introduction

Low-temperature polycrystalline Si (LTPS) TFT is facing a new momentum due to active matrix organic light emitting diode (AMOLED) displays [1-2]. High and uniform performances of LTPS TFT characteristics are well suited for the TFTs in the pixels for AMOLED displays [2]. For AMLCD, on the other hand, since LTPS has a potential to achieve the ultimate displays such as the system-on-panel (SOP) [3-4], LTPS TFT-LCD has been implemented in various electronic devices, such as, hand-held phone (HHP), personal digital assistant (PDA), digital video/still camera (DVC/DSC), and even Note PCs.

For small- and medium-size display applications, LTPS TFT-LCD has advantages over a-Si TFT-LCD [3]. First of all, LTPS TFT-LCD can produce a symmetric panel layout due to the integration of gate driver circuits. Secondly, because there is no severe limitation for the IC bonding pitch as we often

observed in tape-carrier package (TCP) or chip-on glass (COG), LTPS TFT-LCD could provide higher resolution displays. In addition, a low-power consumption, a higher reliability due to reduced number of connections to the outside circuitry, and a higher uniformity of LCD are the advantages over a-Si TFT-LCD.

For large-size display applications, such as note-PCs and monitors, due to decreasing of the percentage of the IC cost over the total cost, large number of photo-masks and CMOS processed LTPS TFT-LCD would not be as competitive as a-Si TFT-LCDs.

In this paper, recent trends of LTPS TFT technology are reviewed. Along with the process and crystallization technique comparisons, a recent development of high-resolution, 5.0-inch LTPS TFT-LCD is presented. In order to efficiently reduce the power consumption of the system, an advanced transflective technique and a multiplexing driving technique are utilized.

| Process                        | LTPS TFT (Bottom Gate, a-Si TFT)    | LTPS TFT (Top Gate)                |  |

|--------------------------------|-------------------------------------|------------------------------------|--|

| Differences                    | - Low H content a-Si & ELA          | - Buffer & Gate Oxide: SiO2        |  |

|                                | - Ion Doping& Activation:ELA/ RTA   | - LDD: Ion Implantation            |  |

| Process                        | - Clean gate SiO2/poly-Si interface | - Relatively wide ELA margin       |  |

| Characteristics                | - One step ELA                      | - Self-align: Small parasitic cap. |  |

|                                | - Narrow ELA margin                 | - Complicated Process              |  |

| No. of Mask                    | - 5 for transmissive (TM)           | - CMOS: 7 for TM, 8 for TF         |  |

|                                | - 7 for transflective (TF)          | - PMOS: 5 for TM, 6 for TF         |  |

| Active                         | PE-CVD a-Si:H                       | LPCVD or PE-CVD a-Si:H             |  |

| Gate Insulator                 | SiNx SiO2                           |                                    |  |

| Inter-Insulator                | SiNx, Organic Layer                 | SiO2/SiNx, Organic Layer           |  |

| Mobility (cm <sup>2</sup> /Vs) | < 1 (for a-Si TFTs)                 | 50~150                             |  |

| Driver Circuits                | N-MOS (ASIC, CMOS)                  | PMOS,NMOS,CMOS                     |  |

| Max. Proc.Temp.                | 370℃                                | 450 ~ 500 ℃                        |  |

Table 2. High performance integrated device trend with respect to the TFT characteristics

| Mobility(cm <sup>2</sup> /Vs) | 80                | 100 ~ 150                                           | 150 ~ 300                                      | >300                       |

|-------------------------------|-------------------|-----------------------------------------------------|------------------------------------------------|----------------------------|

| Uniformity                    | μ :±10%,Vth:±0.5V | $\mu : \pm 5\%, Vth: \pm 0.4V$                      | $\mu : \pm 2\%, Vth: \pm 0.3V$                 | μ :< 1%,Vth:< 0.1V         |

| Design Rule(um)               | 4                 | 2~4                                                 | 1~2                                            | <1                         |

| Integrated Level              | Analog D-Circuits | Digital D-Circuits                                  | Graphic I/F,T-Con.                             | CPU Level                  |

| Driving Speed                 | 3M                | 5M ~ 20M                                            | 20M ~ 40M                                      | 100M                       |

| Driving Circuits              | S/R, L/S          | 6bit DAC, Latch,<br>DC-DC Converter,<br>2bit Memory | 8bit Memory,<br>High Speed Digital<br>Circuits | 64bit Memory,<br>32bit CPU |

#### **Process Review**

Table 1 shows the process comparison between bottom-gate (as well as a-Si TFT) and top-gate LTPS TFTs. One of the big advantages of bottom gate process would be the consecutive deposition process inside the vacuum, such as gate dielectric, active Si, and the inter-insulator. Using this method, the interface between Si and the gate insulator can be well protected.

## Integrations for Display

Table 2 shows a high performance integrated device trend with respect to the TFT characteristics. This could be a roadmap for the ideal TFT-LCD. It is important to note that not only the performance of the TFTs, but also the design rule of the TFT process plays a key role for the development of displays. Currently, 1.5um-design rule photolithographic equipment is available.

## Crystallization

Crystallization technique could be the one of the most critical technologies for the differentiation of the LTPS technology. Nowadays, ELA is the most easily available technique for the industry and research institutions. The typical multiple-pulse grain growth (MPGG) [5] can be used for low-level of integrated circuit devices where high performance TFTs are not required. However, in order to compete with existing a-Si TFT technology, the conventional line-beam ELA method needs to be improved. Recently, laser makers are developing new ideas of laser, such as a dual beam system

coupled with solid-state lasers. Table 3 summarizes the major crystallization methods for LTPS. SLS technique is a relatively new method but the most attractive point is that the flexibility of the process. Depending on the system, SLS process can easily control the desired poly-Si microstructures within a same processing panel. Most of all, the SLS system does not requires the vacuum equipments. Continuous Grain Si (CGS) technique is known as an advanced kind of the metal-induced crystallization (MIC) technique. MIC could be an attractive candidate for the future LTPS due to the fact that the process does not require the expensive excimer lasers. CGS, however, is known to use the excimer laser after solid phase crystallization.

## 5.0" WVGA LTPS TFT-LCD

For the a-Si film, as a pre-cursor, LPCVD is Conventional MPGG technique with linebeam annealing was used to crystallize a-Si thin film In order to achieve high-quality TFT [5]. performances, the condition of the interface before and after Si layer has to be perfectly cleaned and precisely controlled. TEOS-based SiO<sub>2</sub> is used for the high-quality gate dielectric layer. Followed by gate metal formation, ion-implantations were conducted for source and drain of n- and p-channel TFTs and LDD for n-channel TFTs. irradiations were performed for the activation. According to our results, we do not observe any serious damages at the junction of TFTs due to the laser activation. The choice of dielectric as a passivation layer becomes stricter as the display

Table 3. Major Crystallization Methods for LTPS TFTs

|                                | ELA                          | SLS               | CGS                                       |

|--------------------------------|------------------------------|-------------------|-------------------------------------------|

| Beam Shape                     | Line                         | Rectangle         | Line/Rect.                                |

| Beam Size                      | 365 ′ 0.4 (mm <sup>2</sup> ) | 30 ´ 1.5 (mm²)    | 365 ' 0.4 (mm <sup>2</sup> )<br>(600x720) |

| No. of Shots                   | 20                           | Min. 2            | MIC+ ELA                                  |

| Throughput                     | A                            | A/2               | N/A                                       |

| Quality of p-Si                | Random & Small               | Near Single x-tal | Near Single x-tal                         |

| Mobility (cm <sup>2</sup> /Vs) | 50~100                       | 200~550           | 300~550                                   |

| Uniformity                     | ~10%                         | ~5%               | N/A                                       |

| Process Window                 | Sensitive to Condit'n        | Wide Proc. Window | N/A                                       |

| Feasibility                    | Used in Production           | Under development | Used in Production                        |

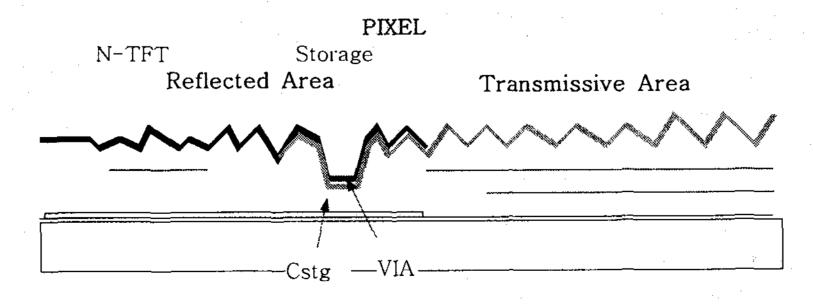

requires higher resolution. Here, for transflective type LCDs, an embossed and photo-definable organic insulator has been used to maximize the brightness and contrast ratio. On top of thick embossed organic layer, reflector layer was sputtered partially as a pixel electrode.

| Table 4. | Specification | of 5.0" | LTPS | TFT-LCD |

|----------|---------------|---------|------|---------|

|----------|---------------|---------|------|---------|

| Item              | Specifications    |

|-------------------|-------------------|

| Display Size      | 5.0" Diagonal     |

| Number of Pixels  | 800x480xRGB       |

| Number of Colors  | 260K              |

| Pixel Pitch       | 45.5μm x 135.5 μm |

| Reflectivity      | 10 %              |

| Brightness        | 60 cd/m2          |

| CR                | 70:1              |

| Aperture Ratio    | 84.5%             |

| Power consumption | 100mW             |

The display performances and brief specifications of the reflective LTPS TFT-LCD are shown in Table 4.

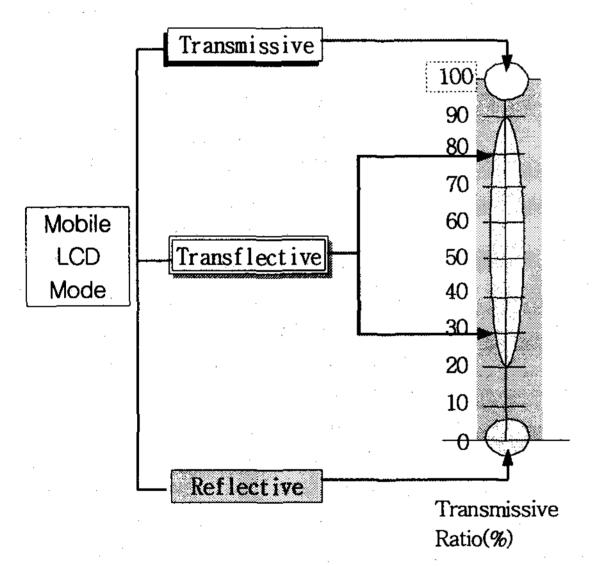

Figure 1. Schematic diagram for transmissive, reflective, and transflective modes for LCD

Figure 1 shows the schematic differences between transmissive, reflective, and transflective

modes. For the transflective mode, by changing the relative area ratio of the pixel, display quality can be optionally optimized depending on the light environments. This is one of the most effective ways to meet both the low-power consumptions and bright LCD for mobile displays such as PDA and HHPC.

## **LCD** Driving

Depending on the performance of LTPS TFTs in the integrated driver circuitry, the driving scheme including digital or analog, point or block addressing, degrees of multiplexing, and the integration level is decided.

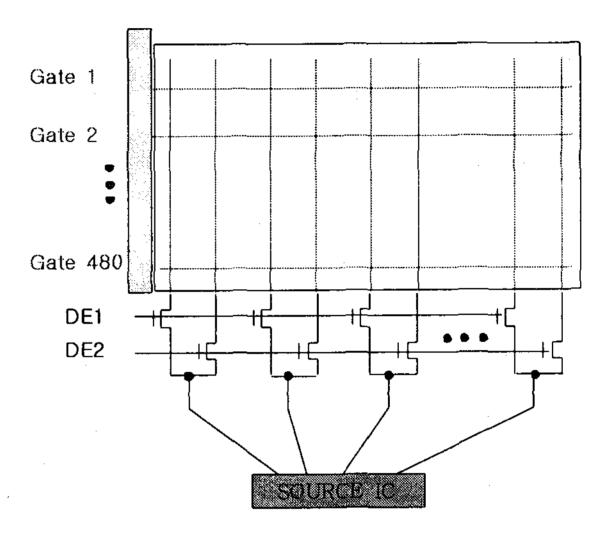

Figure 2. Schematic diagram of the 5.0" LTPS TFT-LCD

Figure 5 demonstrates a schematic block diagram of the 5.0" LTPS TFT-LCD. In order to meet the allocated writing time and reduce the operational frequency of the column driver while meeting the requirement of low power consumption, we employed the multiplexing driving scheme. Based on the panel specification and the TFT simulations, we were able to adopt 2:1 multiplexing scheme. In order to secure a charging margin and a higher image quality of the LCD, the display is driven with frequency of 57.6KHz and an operational voltage range of around 15V.

Figure 3. Cross-section view of a transflective LTPS TFT

## Transflective TFT-LCD

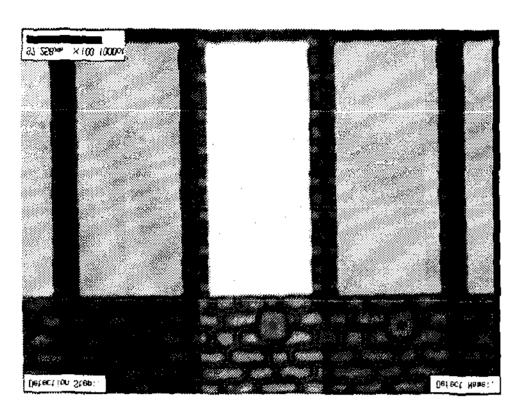

Fig. 4 shows the RGB pixels of the 5.0" LTPS transflective display. The transmissive window is maximized to enhance the panel transmittance. The reflector is positioned on top of the storage capacitor and along the data lines.

Transparent organic layer is used for micro-lens formation for reflected area. Since the reflective light passes through the color filter twice, the color

Figure 4. RGB pixel microstructures for transflective LTPS TFT-LCD

saturation of the reflective mode is twice than that of the transmissive mode. We need to compensate the color saturation between reflective and transmissive mode. There are several ways to compensate the color saturation. One method is to differentiate the color filter thickness between reflective and transmissive windows. Slit masked R, G, B mask only at the reflective windows area can be used for achieving the two-tone color filter.

In the case of transflective mode, the simultaneous maximization of the reflectance and transmittance is essential. For the 90-degree twist

angle condition, compared to the transmissive mode, only 50% transmittance can be obtained. There are several ways to optimize the reflectance and transmittance at the same time.

#### Conclusion

We have developed an 186ppi LCD, one of the world highest resolutioned LTPS TFT-LCDs for HHPC applications. A 5.0" with a 45.5 um x 135.5 um pixel has used the dual gate and LDD structure for the pixels and some of the high-voltage operated TFTs in the integrated drivers. In order to achieve brighter and higher reflectivity of the panel, we have used advanced transflective techniques. The reflectivity of 10% and the contrast ratio of 70:1 were achieved.

## References

- [1] G. Rajeswaran, "Active Matrix OLED Displays: Current Status and Technology Scale-up Issues", AMLCD'02 Digest, 72 (2002)

- [2] T. Sasaoka, M.Sekiya, A. Yumoto, J. Yamada, T.Hirano, Y.Iwase, T.Yamada, T.Ishibashi, T.Mori, M.Asano, S.Tamura, T.Urabe, "A 13.0-inch AM-OLED Display with Top Emitting Structure and Adaptive Current Mode Programmed Pixel Circuit(TAC)", SID'01 Digest, 384 (2001)

- [3] M.Senda, Y.Tsutsui, R.Yokoyama, K.Yoneda, "Ultra-Low-Power Polysilicon AMLCD with Full Integration", SID'02 Digest, 790 (2002)

- [4] T. Morita, H. Kimura, Y. Hanazawa, T. Tsunashima, T. Maeda, N. Moriyama, "A 2.15 inch QCIF reflective color TFT-LCD with integrated 4bit DAC driver". IDW'00, 1149, (2000)

- [5] H.J.Kim "Excimer-Laser Crystallization for Low-Temperature Polycrystalline Si TFTs", KIDS'00, 1243 (2000)