# Modeling of Arbitrary Shaped Power Distribution Network for High Speed Digital Systems

Seong-Geun Park, Jiseong Kim\*, Jong-Gwan Yook, Han-Kyu Park

Dept. of Electrical and Electronic Eng., Yonsei Univ., Korea,

khen@yonsei.ac.kr, jgyook@yonsei.ac.kr

\*R&D Group, Computer Division, Samsung Electronics, Korea, jkim@samsung.com

#### **Abstract**

For the characterization of arbitrary shaped printed circuit board, lossy transmission line grid model based on SPICE netlist and analytical plane model based on the segmentation method are proposed in this paper. Two methods are compared with an arbitrary shaped power/ground plane. Furthermore, design considerations for the complete power distribution network structure are discussed to ensure the maximum value of the PDN impedance is low enough across the desired frequency range and to guide decoupling capacitor selection.

Key words: power integrity, power/ground plane, segmentation method, lossy transmission line, simultaneous switching noise, EMI, decoupling capacitor

#### I. INTRODUCTION

In today's high-end computer system, with increasing clock rate and decreasing power supply voltage, the delivery requirement for the power distribution networks (PDN) has greatly increased and the tolerance to noise has become more critical issue. The PDN must provide steady supply voltage in the presence of very large AC current demands within a specified range (typically ± 5% or below) at all frequency range to avoid excessive simultaneous switching noise (SSN) and ground bounce and to reduce electromagnetic interference (EMI) risk [1]. Power/ground plane with properly located highfrequency decoupling capacitors can control PDN impedance, and a few works have been done to model a pair of solid power/ground planes in a simple rectangular shape by means of a transmission line grid method or analytical plane-impedance method. [2][3]

In this paper, accurate and efficient modeling methods are proposed for the characterization of arbitrary shaped PDN to deliver low input impedance, specially in high frequency region. In the first approach, the complex geometry is modeled with analytical expression derived from the segmented planes consisted with several group of sub-planes of the rectangular shapes. In the second method, irregular shaped power plane is modeled with networked transmission lines and its electrical

characteristics are simulated with SPICE. The accuracy of two methods is verified by comparing with each other. Finally, this paper discusses about design considerations for complete PDN structure, including voltage regulator module (VRM) and decoupling capacitors.

#### II. MODELING METHODOLOGY

### A. Analytical plane model using segmentation method

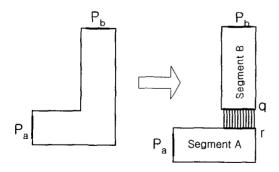

The analysis of arbitrary-shaped plane can be extended to that geometry which results from the connection of rectangular shapes. The basic structure in Fig.1(a) can be decomposed into the cascade of two sub elements for which the impedance matrix can be obtained from Green's function of rectangular segments. The generic impedance between any two ports on the plane is given by [4]. Using the cavity modes, the impedance between ports "i" and "j" can be represented as

$$Z_{ij} = j\omega\mu T \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \frac{\varepsilon_m^2 \varepsilon_n^2}{(k_{mn}^2 - k^2)ab} f(x_{i,} y_i) f(x_j, y_j)$$

where

$$f(x_i, y_i) = \cos\frac{2m\pi x_i}{2a} \operatorname{sinc}\frac{m\pi t_{xi}}{2a} \cos\frac{2n\pi y_i}{2b} \operatorname{sinc}\frac{m\pi t_{yi}}{2b}$$

$$k_{mn}^{2} = \left(\frac{m\pi}{a}\right)^{2} + \left(\frac{n\pi}{b}\right)^{2}$$

$$k = k^{j} - jk^{jj} \quad k^{jj} = \omega\sqrt{\mu\varepsilon}\left((\tan\delta)/2\right) + (r/(2T))$$

In the above equation, plane dimension is a x b, the parameter T is the thickness of the dielectric.  $(x_i, y_i)$  and  $(x_j, y_j)$  are the coordinates of the port locations,  $(t_{xi}, t_{yi})$  and  $(t_{xj}, t_{yj})$  are dimension of the ports, =1 for m=0 and n=0; for m=0 or n=0; 2 for m≠0, n≠0. m,n are propagating modes on the cavity,  $\mu$ , $\epsilon$  are the permeability and permittivity of the medium, respectively,  $\omega$  is the angular frequency and  $Z_{ij}$  is the impedance between the *i*th and *j*th ports.  $\tan\delta$  is the loss tangent of the dielectric material,  $r = \sqrt{2/\omega\mu\sigma}$

In which  $\sigma$  is the conductivity of the metallization. Finally, the overall Z-matrix of Fig.1(a) can be expressed as

$$\begin{split} & [Z] = \begin{bmatrix} Z_{AB11} \\ [Z_{AB21}] \end{bmatrix} \begin{bmatrix} Z_{AB12} \\ [Z_{AB22}] \end{bmatrix} \\ & [Z_{AB21}] = \begin{bmatrix} Z_{P_a} \end{bmatrix} - \begin{bmatrix} Z_{P_{aq}} \end{bmatrix} [[Z_{qq}] + [Z_{rr}]]^{-1} [Z_{qp_a}] \\ & [Z_{AB12}] = \begin{bmatrix} Z_{P_{aq}} \end{bmatrix} [[Z_{qq}] + [Z_{rr}]]^{-1} [Z_{rp_b}] \\ & [Z_{AB21}] = \begin{bmatrix} Z_{P_{rr}} \end{bmatrix} [[Z_{qq}] + [Z_{rr}]]^{-1} [Z_{qp_a}] \\ & [Z_{AB22}] = \begin{bmatrix} Z_{P_b} \end{bmatrix} - [Z_{P_{br}}] [[Z_{qq}] + [Z_{rr}]]^{-1} [Z_{rp_b}] \end{split}$$

Consider the structure as shown in Fig.1(b) where an irregular shaped geometry can be broken down into the several rectangular segments. It is assumed that the port size is infinitesimally small, and the boundaries are opened at the edges. The impedance matrix element have double infinite series, which for practical calculation must be truncated, so the instead of infinite series, finite summation limit can be used.

Fig.1(a) The Application of segmentation method to two elements

Fig.1(b) Arbitrarily shaped power and ground planes (test board)

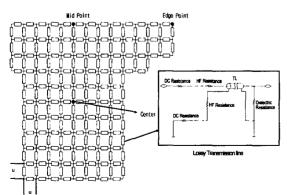

#### B. lossy transmission line grid model with spice

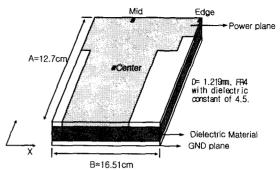

In this section, the irregular shaped power/ground plane is simulated by transmission line grid equivalent circuit with SPICE. A pair of parallel planes can be modeled by a grid of transmission line equivalent circuits [3]. The low-frequency equivalent components of the planes can be derived from a quasi-static model. We first define the length of u of a square unit cell as shown in Fig. 2, which should be equal to or less than 10% of the shortest wavelength of interest. The cell size u is selected such that we have an integer N<sub>x</sub> and N<sub>y</sub> number of cells along the x and y direction, respectively. For every unit square of the plane with side dimensions of u. plane separation (dielectric height) of D, the static plane capacitance C and propagation delay along the edge TD can be computed. From the capacitance and delay, an equivalent characteristic impedance Z<sub>tline</sub> inductance L of the unit cell can be calculated as:

$$C = \varepsilon_0 \varepsilon_r \frac{u^2}{D}, TD = \frac{u\sqrt{\varepsilon_r}}{c},$$

$$Z_{tline} = \frac{TD}{C} = \sqrt{\frac{L}{C}}, L = Z_{tline} * TD = \mu_0 D$$

where  $\mathcal{C}$  is the speed of light (3 x  $10^8$  m/s), and the DC resistance  $R_{de}$  parameter is the resistance of both the power and ground planes for a steady DC current, where the planes are assumed to be uniform. The unit cells are replaced by four transmission lines along the edges of unit cells, each transmission line representing the same delay but only one quarter of the area, thus having an impedance of 4  $Z_{tline}$ . Inside the equivalent grid, where the sides of unit cells touch, two transmission lines are connected in parallel, reducing the characteristic impedance to 2  $Z_{tline}$ . Along the outer edges, the unit-cell transmission lines are standing alone. The parameters for the edge ( $Z_{edge}$ ,  $TD_{edge}$ ) and grid ( $Z_{grid}$ ,  $TD_{grid}$ ) transmission lines are given as:

$$Z_{edge} = \frac{4}{\sqrt{2}} Z_{tline}, \ TD_{edge} = \frac{1}{\sqrt{2}} TD,$$

$$Z_{grid} = \frac{2}{\sqrt{2}} Z_{tline}, \ TD_{grid} = \frac{1}{\sqrt{2}} TD$$

The  $\sqrt{2}$  correction factor is used to match the equivalent circuit's delay and impedance along the x and y axes. In addition, the lossy parameters should be considered for accurate modeling. The high frequency resistance  $R_{hf}$  accounts for skin effect both on top and bottom conductors, and the shunt conductance G represents the dielectric loss in the material between the planes. The frequency dependent parameters, such as  $R_{hf}$  and G, are taken into account by cadence PSPICE Analog Behavioral Model (ABM), which specifies the form of the S-domain transfer function. The lossy parameters of a unit cell can be computed as:

$$R_{dc} = \frac{1}{\sigma T}, \ R_{hf} = \sqrt{\frac{\omega \mu_0}{2\sigma}}, \ G = \omega C \tan \delta$$

where T is conductor thickness and  $tan\delta$  is the loss tangent of the material, which is assumed to be frequency independent. The equivalent modeling of irregular shaped power/ground plane is created with square cells. Accordingly it can be easily simulated by transmission line grid equivalent circuit with SPICE. Equivalent modeling for Fig. 1(b) can be modeled as shown in Fig. 2. The granularity (number of unit cells) of the model has implications on accuracy modeling for physical irregular shape and run time. A dense array of unit cells will give a more accurate solution for complex structure. But the number of transmission line segments required may become very large. As a result, large memory requirements and a considerable CPU run time are required for analysis.

Fig.2 transmission line grid model

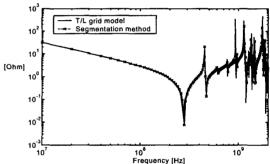

### C. Comparison between spice and analytical plane models

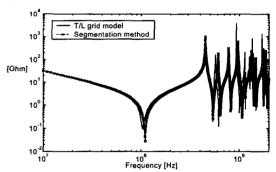

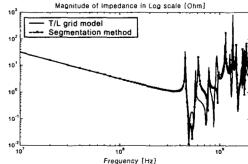

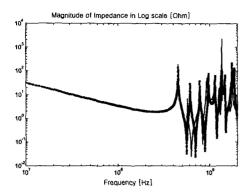

To compare the results derived from two independent approaches described above, an arbitrary shaped power and ground plane shown in Fig.1(b) has been simulated. From the dimensions and parameters of the planes, magnitude of self impedance and transfer impedance between center and the other port were computed as shown in Fig.3(a),(b),(c) and (d). Due to the many boundaries in the structure, the resonant frequencies for an irregular shape plane occur more than the rectangular plane. The results of self impedance shows that the transfer impedance data are inaccurate in high frequency region, but good agreement in other frequency region.

Fig.3(a) Magnitude of self impedance at the center

Fig.3(b) Magnitude of self impedance at the edge

Fig.3(c) Magnitude of transfer impedance between the center and mid point

Fig.3(d) Magnitude of transfer impedance between the center and edge point

## III. SIMULATION OF COMPLETE PDN SYSTEM

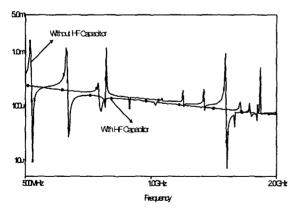

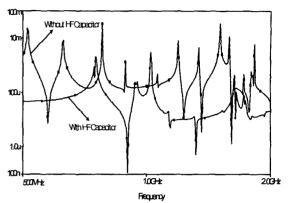

In this section, the PDN structure, encompassing VRM, high performance microprocessor, bulk and high frequency ceramic capacitors modeled with extended RLC circuits including via holes, is simulated with SPICE. The processor model is designed by [5], and the linear model for the VRM is proposed in [6]. The impedance characteristics are improved by high frequency capacitors (ceramic capacitors 1uF - 24ea, 100nF - 10ea) in complete PDN structure as clearly shown in Fig. 4.

Fig.4(a) Impedance magnitude at the processor pin of complete PDN  $\,$

Fig.4(b) Impedance at the mid point of complete PDN

#### IV. CONCLUSION

This paper presents simulation and analysis methods of the irregular-shaped power/ground plane for the high speed digital systems their accuracy has been proved by comparing each other. Further, the design of the PDN structure, including VRM, bulk capacitors, high frequency ceramic capacitors, and microprocessor, has been described. The proposed methodology can be applied to predict the impedance over the desired frequency range and to guide proper decoupling capacitor selection.

#### REFERENCES

- [1] Herrell D and Beker B, "EMI and power delivery design in PC systems," *IEEE 6th Topical Meeting on Electrical Performance of Electronic Packaging*, pp. 23-26, 1997.

- [2] L. D. Smith, Anderson R and Roy T, "Power Plane SPICE Models and Simulated Performance for Materials and Geometries," *IEEE Trans. on Advanced Packaging*, Vol. 24, Issue 3, pp. 277–287, Aug. 2001.

- [3] Nanju Na and Madhavan Swaminathan, "Modeling and Transient Simulation of Planes in Electronic Packages for GHz systems," 1999 international Conference on Computer Design, Oct. 1999.

- [4] Rakesh Chadha and K. C. Gupta, "Segmentation Method Using Impedance Matrices for Analysis of Planar Microwave Circuits," *IEEE Trans. Microwave Theory Tech.*, Vol. MTT-29, pp. 71~74, Jan. 1981.

- [5] Intel Corporation, Intel Pentium 4 Processor / Intel 850 Chipset Platform Design Guide, Aug. 2001.

- [6] L. D. Smith and Anderson R., "Power Distribution System Design Methodology and Capacitor Selection for Modern CMOS Technology", *IEEE Trans. on Advanced Packaging*, Vol. 22, Issue 3, pp. 284–291, Aug. 1999.