## LSI Packaging Technologies for High-End Computers and Other Applications

**Tatsuo Inque**

# LSI Packaging Technologies for High-End Computers

Computer Packaging Devices Dept. NEC Ibaraki Ltd.

## **Contents**

- 1. Introduction to High-End Computers

- 2. Trend of LSI Packaging Technology for High-End Computers

- 3. LSI Packaging Technologies in NEC's High-End Computers

- Inter-Layer Transfera of Wiring Substrates as Packaging Devices

- Future Aspect of LSI Packaging Technology

- 6. Summary

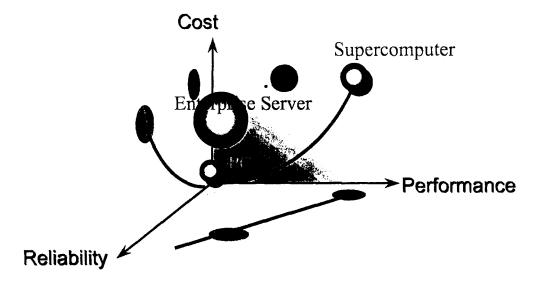

■ Positioning Categorized Computers in Tree Dimensional Space of Cost, Performance and Reliability

## 1. Introduction to High-End Computers

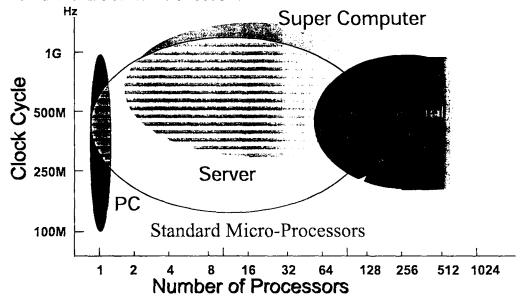

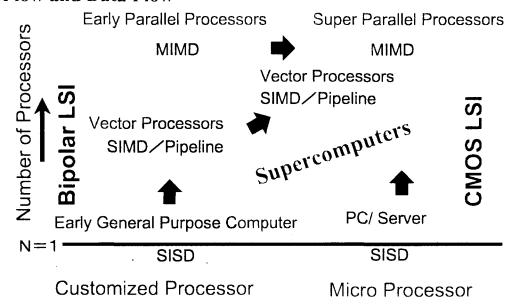

■ Comparison between Categorized Computers in Clock Cycle and Number of Processors

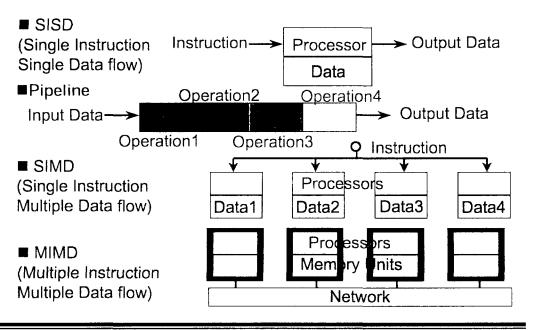

■ Comparison between Categorized Computers in Instruction Flow and Data Flow

### 1. Introduction to High-End Computers

■ Categorizing Computers in Instruction Flow and Data Flow

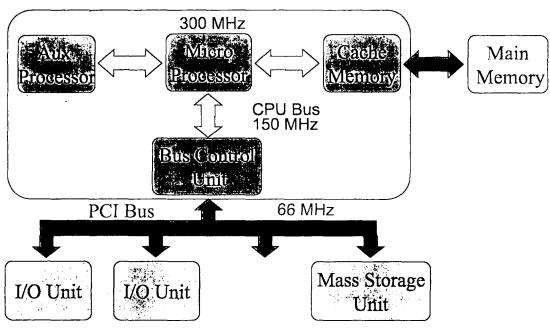

**■** Architecture of Personal Computer

## 1. Introduction to High-End Computers

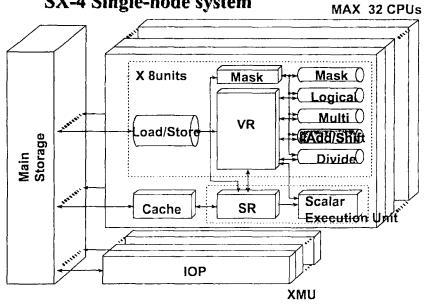

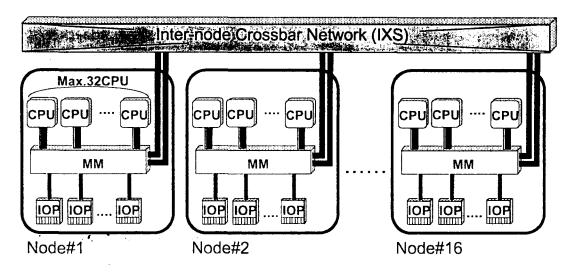

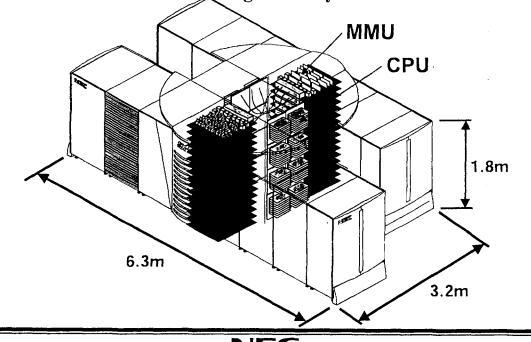

■ Architecture of Vector Supercomputer SX-4 Single-node system MAX

#### ■ Architecture of Vector Supercomputer

## SX-4 Multiple-node system

## 2. Trend of LSI Packaging Technology for High-End Computers

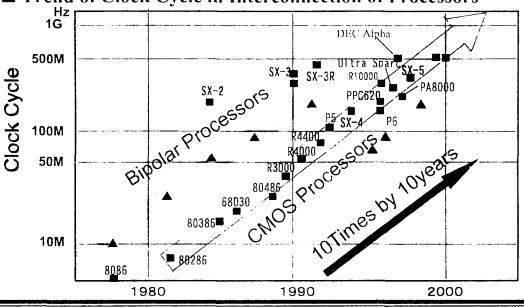

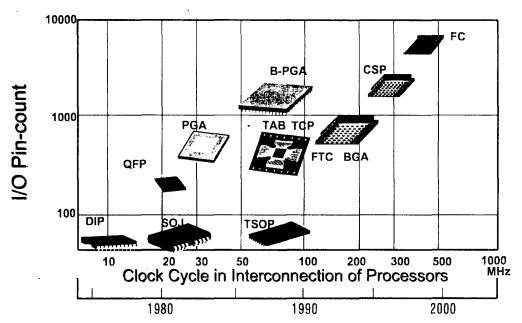

■ Trend of Clock Cycle in Interconnection of Processors

## 2. Trend of LSI Packaging Technology for High-End Computers

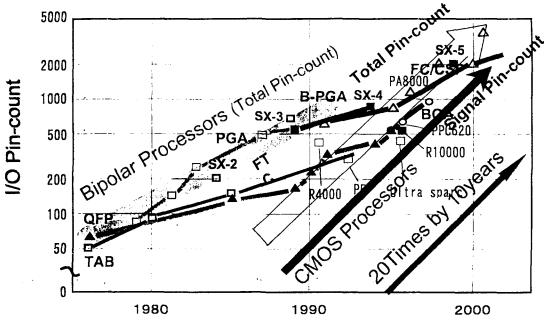

■ Trend of I/O Pin-count in LSI Package for Processors

## 2. Trend of LSI Packaging Technology for High-End Computers

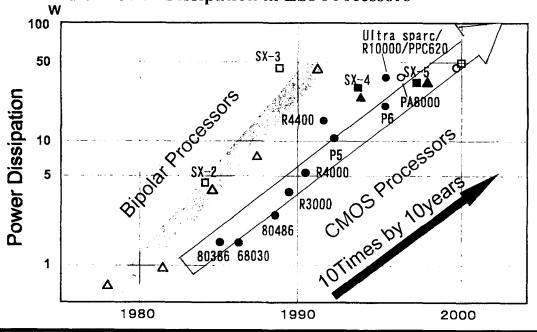

■ Trend of Power Dissipation in LSI Processors

## 2. Trend of LSI Packaging Technology for High-End Computers

## **■** Trend of LSI Package for Processors

## 2. Trend of LSI Packaging Technology for High-End Computers

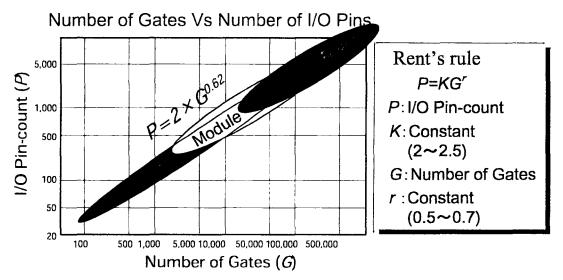

■ "Rent's Rule, A Study in Relation between Scale of Integration and I/O Pin-count

## 3. LSI Packaging Technologies in NEC's High-End Computers

■ Schematic view of SX-5 single node system

- 3. LSI Packaging Technologies in NEC's High-End Computers

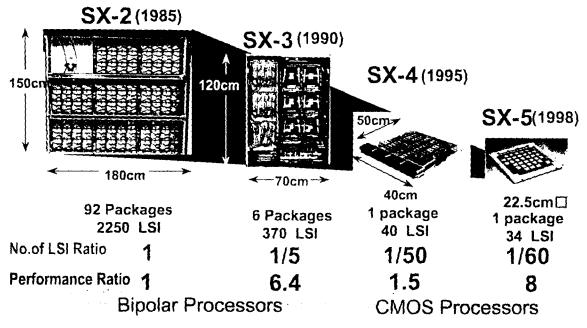

- Transition in Technology for NEC's Supercomputers

- 3. LSI Packaging Technologies in NEC's High-End Computers

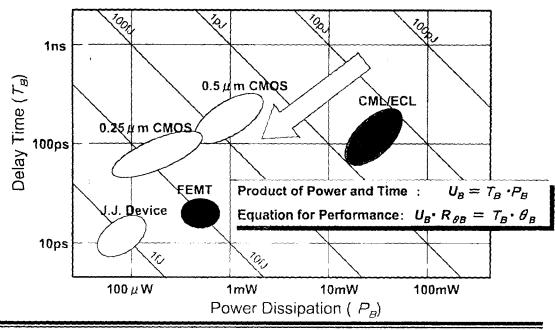

- **■** Comparison in Power and Delay of Switching Devices

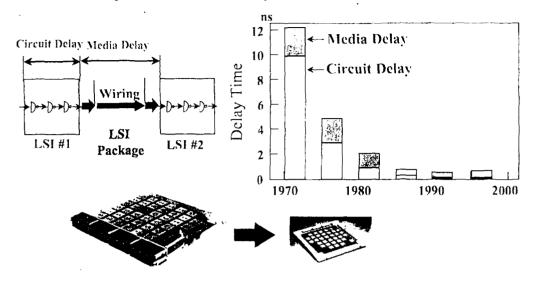

#### ■ Circuit Delay and Media Delay

Higher density of LSI package reduces Media Delay, it also brings higher heat density. It causes higher error rate in operating electronic devices.

#### 3. LSI Packaging Technologies in NEC's High-End Computers

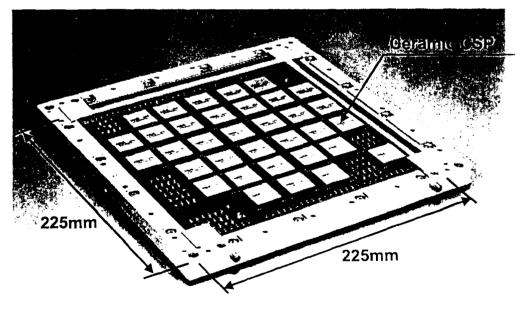

■ CPU Package (MCP) of NEC SupercomputerSX-5

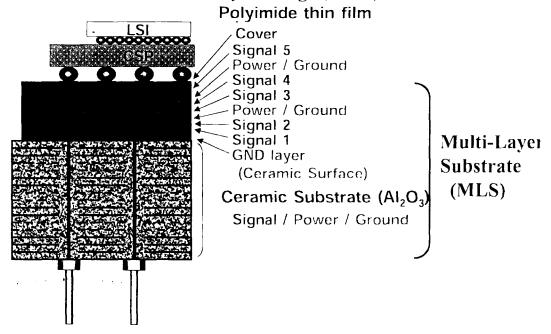

#### ■ Cross Section of Multi-Chip Package (MCP)

### 3. LSI Packaging Technologies in NEC's High-End Computers

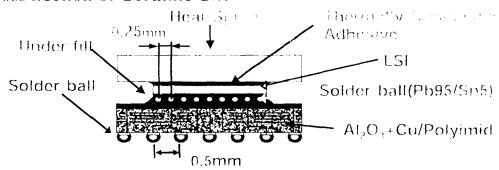

#### **■** Cross Section of Ceramic CSP

Specifications of ceramic CSP

| Size [mm]          | 23 x 23                                       |

|--------------------|-----------------------------------------------|

| No. of I/O pins    | 2009                                          |

| IO pitch [mm]      | 0.5                                           |

| Substrate          | Al <sub>2</sub> O <sub>3</sub> + Cu/Polyimide |

| LSI I/O pitch [mm] | 0.25                                          |

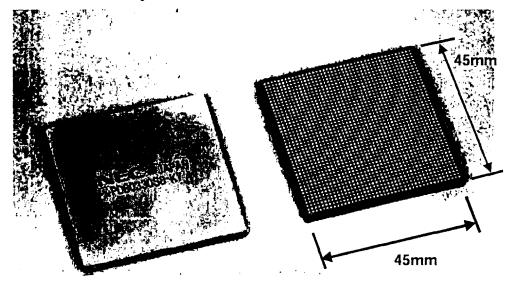

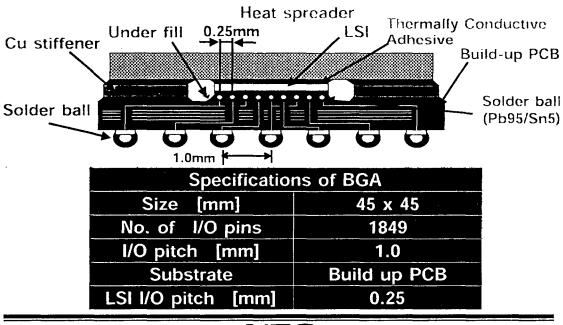

## **■ BGA** for Memory PCB

#### 3. LSI Packaging Technologies in NEC's High-End Computers

#### **■** Cross Section of BGA

■ CPU Package(MCP) for NEC Server iPX7800SV

3. LSI Packaging Technologies in NEC's High-End Computers

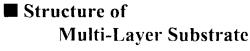

(a) Photograph of Signal Layer (L/S=25/ 25  $\mu$  m)

(b) Cross Section of Polyimide Thin-film Layers

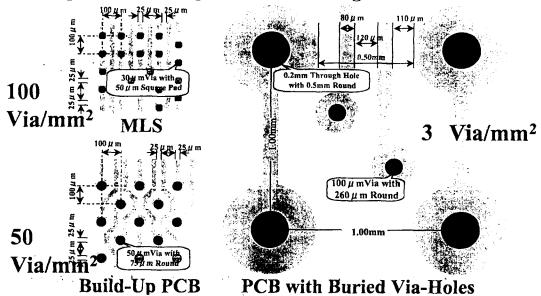

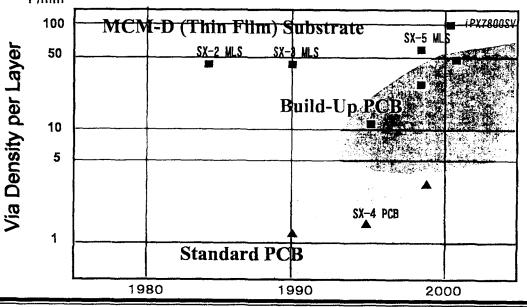

## 4. "Inter-Layer Transferability" of Wiring Substrates as Packaging Devices

■ Comparison of Design Rules for Wiring Substrates

- 4. "Inter-Layer Transferability" of Wiring Substrates as Packaging Devices

- Transition of Inter-Layer Transferability P/mm²

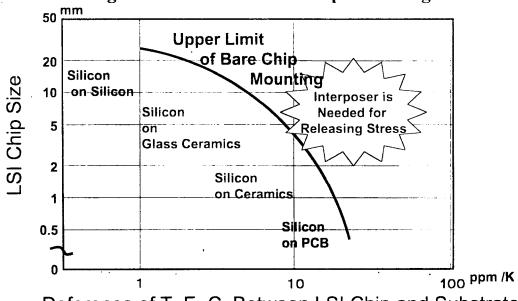

## 5. Future Aspect of LSI Packaging Technology

■ Limit of Rigid Structure for Bare Chip Mounting

Deference of T. E. C. Between LSI Chip and Substrate

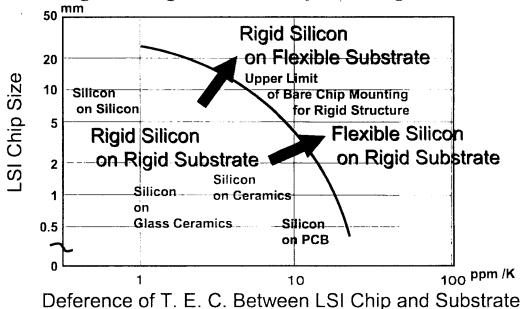

### 5. Future Aspect of LSI Packaging Technology

■ Challenge for Large Size Bare Chip Mounting

5. Detween LSI Only and Substrate

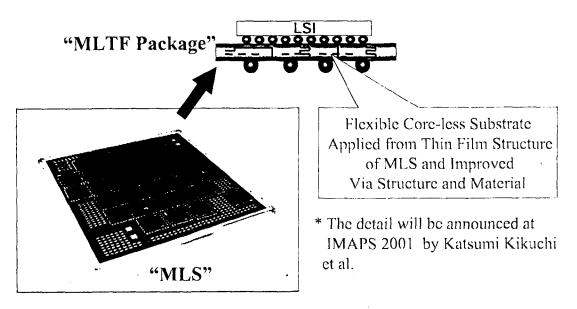

- 5. Future Aspect of LSI Packaging Technology

- "MLTF" Package, an Application of Flexible Substrate

## 6. Summary

- 1. "MLS", state of the art MCM-D wiring substrate.

- 2. High pin-count LSI assembly.

- 3. Higher speed needs higher packaging density.

- 4. Wiring substrate, the key of LSI packaging device.

- 5. "Inter-Layer Transferability", a new index for the performance of wiring substrates.

- 6. "MLTF package", a core-less flexible package for high pin-count LSI.