## A High-speed Max/Min circuit

V. Riewruja, T. Chimpalee, A. Chaikla, S. Supaph

Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang, Ladkrabang, Bangkok 10520, Thailand

(Tel: 66-2-739-1362; Fax: 66-2-326-9989; E-mail: vanchai@cs.enq.kmitl.ac.th)

## **Abstract**

An integrable circuit technique for implementing high-speed analog two-input Max/Min circuit is described. The realization method is suitable for fabrication using CMOS technology. The proposed circuit comprises a current mirror and electronic switch connected with a absolute value circuit. The maximum or minimum operation of the proposed circuit can be selected by an external control voltage. The proposed analog Max/Min circuit has a very sharp transfer characteristic and is suitable for real-time systems. Simulation results verified the circuit performances are agreed with the expected values.

## 1. Introduction

A maximum (Max) and minimum (Min) operations are most frequently used in the fuzzy inference systems. Recently, the applications of the fuzzy inference in industry, robotics, image processing and home electronics are receiving much attention [1]. Usually, the approach of the fuzzy inference systems is implemented in the form of software on digital computers. The processing speed of a digital computer is inefficient for the real-time application. An analog circuit technique can provide the advantage of high-speed operation. The realizations of Max/Min operations in analog circuit form so far have been implemented by using either a second generation current conveyor (CCII) [2] or an operational transconductance amplifier (OTA) [3] as a basic active circuit element. These approaches require diode function as an electronic switch to eliminate undesirable signal to provide Max/Min operations. However, the high-speed performance of these approaches is limited by the delay caused by the transition between "on" and "off" state of diodes. The dynamic range of the Max/Min circuits using OTA are also limited by the input stage of an OTA. Another approach is based on the use of CMOS circuit technique to provide Max/Min circuit [4] The disadvantage of this approach is some of MOS transistors change the operation regions, saturation and nonsaturation region, that causes the distortion on the output signal and limits the operating speed.

The most reported realizations of Max/Min circuits so far have been implemented either maximum or minimum circuits. If both Max and Min circuits can integrate into same circuit scheme, then there are advantages to be gained. The purpose of this article is to propose a CMOS circuit technique for realization of the selectable Max/Min circuit. The proposed circuit consists of a current mirror and electronic switch connected with an absolute value circuit. The realization method can result in high accuracy and high-speed. The maximum or minimum operations can be selected by using an external voltage control.

## 2. Circuit description

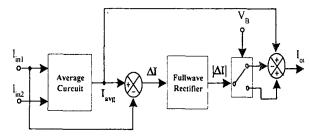

The block diagram of the proposed principle is shown in figure 1. The input current  $I_{in1}$  and  $I_{in2}$  is taken to find average value,  $I_{avg} = (I_{in1} + I_{in2})/2$ . The output current of fullwave rectifier [8] resulted from the difference value of  $I_{avg}$  and  $I_{in1}$ ,  $\Delta I$ . The output current  $I_{out}$  produced by this circuit has two condition, the first condition is the maximum value of the summation of  $I_{avg}$  and  $|\Delta I|$  and the second condition is the minimum value of the difference between  $I_{avg}$  and  $|\Delta I|$ .

Fig. 1. The block diagram of the proposed circuit

Figure 2 shows the circuit that follows by the proposed principle in figure 1. An average value circuit [5-6] comprised two unity current mirrors of the transistors  $M_5 - M_7$  and  $M_8 - M_9$  that provide the summation of  $I_{in1}$  and  $I_{in2}$  through node A. Denote that the transistor  $M_1 - M_4$  form as a current mirror with current gain equal to 0.5 and the transistors are all matched and operated in their saturation region. The drain current of the transistors  $M_3$  and  $M_4$  can