## Flip Chip Applications

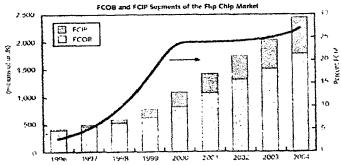

Figure 4. Although growth is expected for both FCOB and FCIP over the next decade, FCIP will account for the majority of the m

MicroElectronic Packaging Lab. (MEPL)

# Worldwide Flip Chip Volumes

### millions

| :           | 1996  | 1997   | 1998   | 1999   | 2000   |

|-------------|-------|--------|--------|--------|--------|

| wristwatch  | 287.7 | 351.1  | 420.8  | 457.3  | 461.1  |

| automotive  | 240.8 | 314.2  | 395.3  | 510.1  | 655.3  |

| pomoia      | 26.8  | 64.7   | 140.3  | 281.4  | 461.1  |

| computer    | 40.1  | 83.2   | 140.3  | 246.3  | 412.6  |

| telcom      | 46.8  | 73.9   | 102.0  | 158.3  | 267.0  |

| display     | 26.8  | 40.0   | 76.5   | 105.5  | 169.9  |

|             | 669.0 | 927.0  | 1275.0 | 1759.0 | 2427.0 |

| Growth Rate |       | 38.50% | 37.50% | 37.90% | 37.90% |

Source: IBM Microelectronics

MicroElectronic Packaging Lab. (MEPL)

Motorola StarTAC Cellular Phone

Source: Prismark

MicroElectronic Packaging Lab. (MEPL)

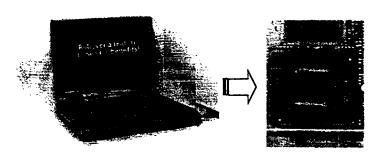

# Production Example - Packaging

### Intel's Mini-Cartridge in Compaq's Armada 7800 Portable Computer

- •5.5 x 5.9 x 0.7 cm

- •Pentium II processor, L2 cache memory and a thermal regulator

- •Pentium II flip chip mounted on a microvia BGA substrate with over 500 I/O

- •BGA mounted onto the Mini-Cartridge module

- Area array connector with 240 solder balls for motherboard attachment

# Packaging - Intel Minicartridge

- □ Pentium II flip chip in BGA

- □ BGA substrate and cartridge board are microvia

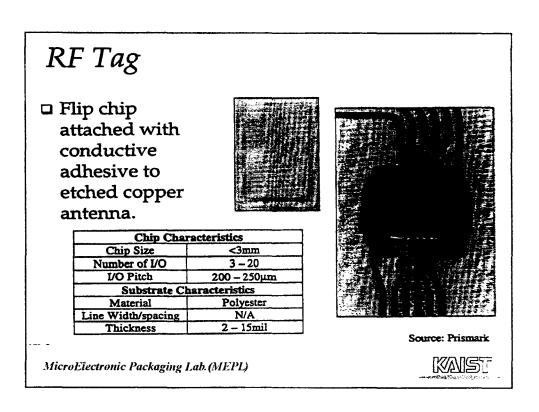

| Chip Cha           | racteristics       |  |

|--------------------|--------------------|--|

| Chip Size          | <40mm              |  |

| Number of I/O      | <5000              |  |

| I/O Pitch          | 150 – 250µm        |  |

| Substrate C        | haracteristics     |  |

| Material           | Ceramic, FR-4, HDI |  |

| Line Width/spacing | 50 – 100μm         |  |

| Thickness          | Largest - 62mil    |  |

MicroElectronic Packaging Lab. (MEPL)

KAIST

# Flip Chip Solder Bump

MicroElectronic Packaging Lab. (MEPL)

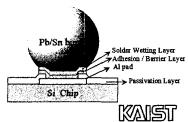

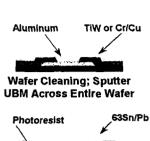

# Flip Chip Under Bump Metallurgy (UBM)

- Excellent adhesion to wafer passivation and bond pad

- Protection of IC metal from environment

- Low resistance between IC final metal and bump

- Effective solder diffusion barrier between final metal and solder alloy

- Solder wettable metal of appropriate thickness

- Dompatibility with probed wafers

MicroElectronic Packaging Lab. (MEPL)

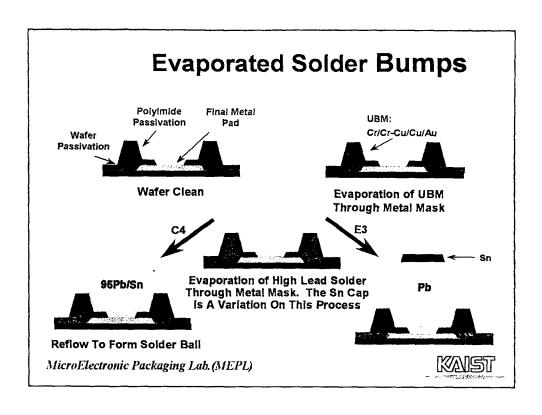

# **Evaporated Solder Bumps Bump Formation**

### In-situ Sputter Clean

### Evaporation of UBM

- · Alignment of Metal Mask to Wafer

- Evaporation of Cr/Cr-Cu/Cu/Au

### Evaporation of Solder

- 95Pb/Sn or 97Pb/Sn

- Height determined by:

- volume of evaporated alloy

- size of mask

- opening /distance between mask and wafer

#### Reflow to Form Solder Ball

MicroElectronic Packaging Lab. (MEPL)

UnderBurny Metal trivuc(A) RM)

Pb/Sn Solder Bump Typ 97/3 or 95/5

Final Metal Pad

### 3

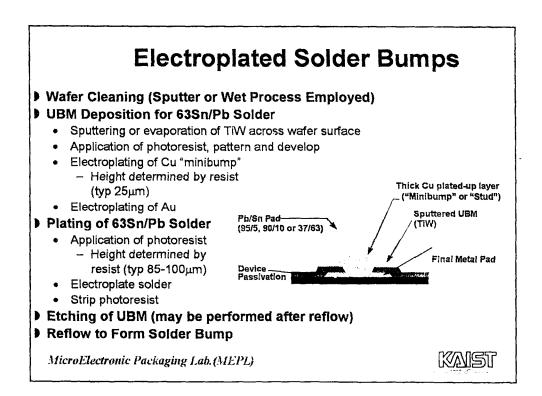

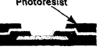

## **Electroplated Solder Bumps**

Apply 2nd Layer of

Apply Photoresist, Pattern and Develop

**Electroplate Thick** Cu Layer; Apply Au

Photoresist, Pattern and Develop; **Electroplate Solder**

Strip Photoresist and **Etch Back UBM** (this step can occur after reflow)

Reflow to Form Solder Ball

MicroElectronic Packaging Lab. (MEPL)

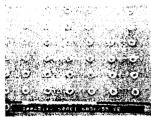

### **Electplated Solder Bump Formation Process** Developed by KAIST MEPLAB

0.me21014 22/12 5298 58 5E Patterned thick PR(40µm)

Plated bump, before reflow

(100 µm ball, 280µm pitch)

After Reflow

MicroElectronic Packaging Lab. (MEPL)

KAYST

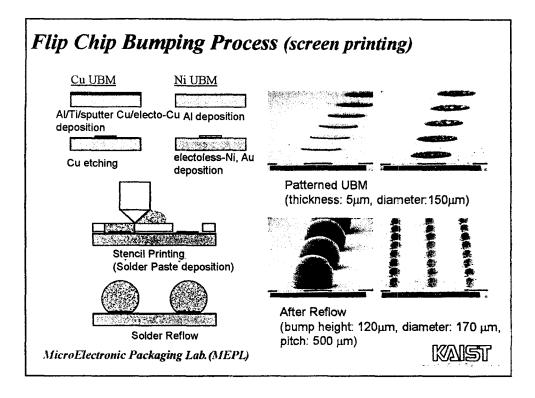

# Solder Paste Screen Printing Bumping Process

Solder Bump-

Device

- In-Situ Sputter Clean

- **UBM Deposition**

- Sputter Al/Ni/Cu across wafer surface

- **UBM Patterning**

- · Apply photoresist, pattern and develop

- · Etching of UBM

- Removal of photoresist

- **▶** Solder Paste Deposition

- Various solder alloys

- Proprietary process

- ▶ Reflow to Form Solder Bump

MicroElectronic Packaging Lab. (MEPL)

Final Metal Pad

Sputtered UBM (AVNI/Cu)

# Solder Paste Screen Printing Bumping Process

In-situ Sputter Clean; Sputter UBM Across Wafer

Apply Photoresist, Pattern and Develop

Etch UBM

Remove Resist

Print Solder (Proprietary Process)

Reflow to Form Solder Ball

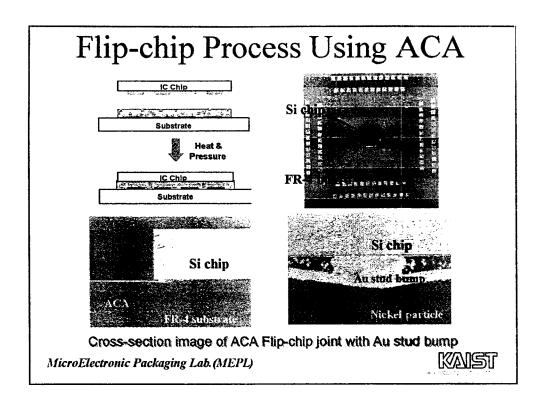

# **Stud Ball Bumping**

### **Description**

- Wire Bonders Create Ball Bond on I/O Pad

- Modification of existing equipment

- Wire is Broken Off Close to Ball Bond

- 63Sn/Pb and Au wire available

- ▶ Ball is Coined For Use With Conductive Adhesives

- Does not provide for self-alignment during assembly

- · Bump does not collapse significantly

- Device requires high contact pressure during assembly

- ▶ Ball Can Also Be Coupled With Eutectic Solder

MicroElectronic Packaging Lab. (MEPL)

# Stud Ball Bumps

Coined Au Stud Bump

PHOTO I SINGLE BUMPS

MicroElectronic Packaging Lab. (MEPL)

KAIST

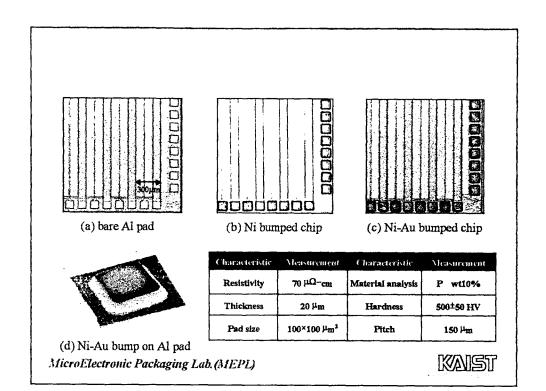

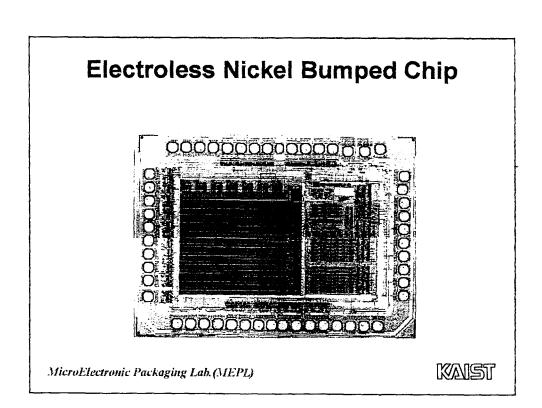

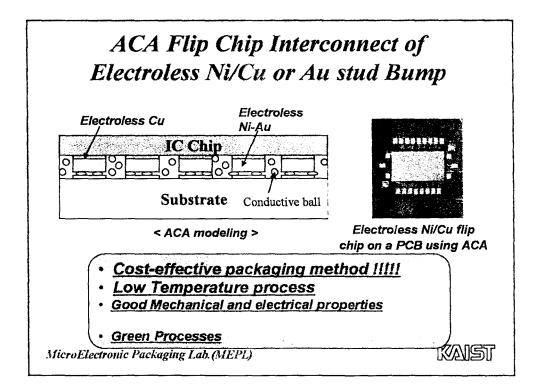

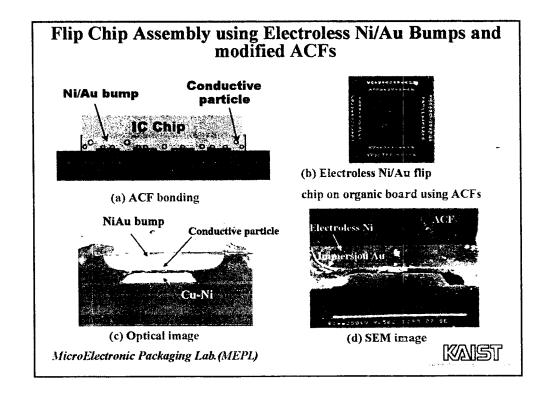

## **Electroless Nickel Bumps**

### **General Features:**

- ▶ Potential to be lowest cost bumping process

- ▶ Least consistent of all processes

- ▶ Pitch dependent upon UBM height required

- ▶ High volume consumer & consumable markets not solution for all wafers and/or products

### UBM (Ni):

- ▶ Good adhesion to final metal

- ▶ Ni does not adhere to passivation

- Very high stress film

- Inability to bump over probed wafers

- ▶ Al Bond pad thickness is reduced 30-40% during zincation

MicroElectronic Packaging Lab. (MEPL)

### **Process Flow**

Zincate

Electroless Nickel plate

· Gold Flash

2

MicroElectronic Packaging Lab. (MEPL)

KAIST

# Electroless Ni Bump by KAIST MEPLAB

MicroElectronic Packaging Lab. (MEPL)

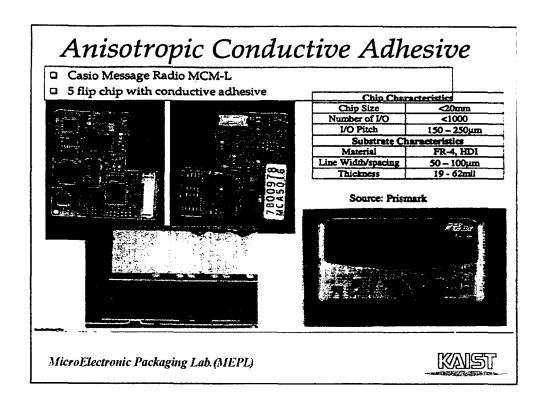

### **Electroless Nickel Bump Applications**

As a bump, the nickel UBM can be used directly with conductive adhesives. - No additional processing is needed.

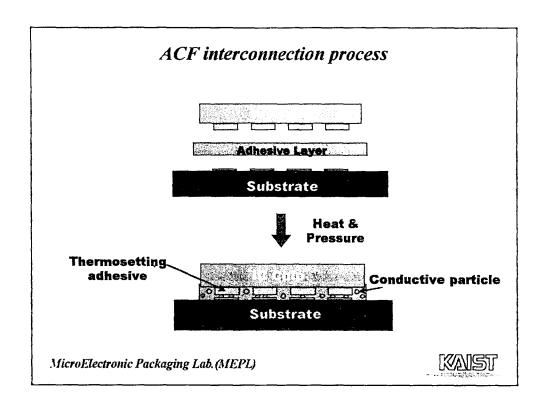

**Anisotropic Conductive Film (ACF)**

MicroElectronic Packaging Lab. (MEPL)

## **Bump Interconnection Techniques**

### 1. Solder bumps - Solder Reflowing

- Evaporated solder bumps

- Electroplated solder bumps

- Screen printed solder bumps

- Solder bumps deposited on wettable metal terminals(UBM) on the chip

- A matching footprint of solder wettable terminals on the substrate (ex. Cu)

- The upside-down(flip chip) alignment to the substrate

- All joints made simultaneously by reflowing the solder

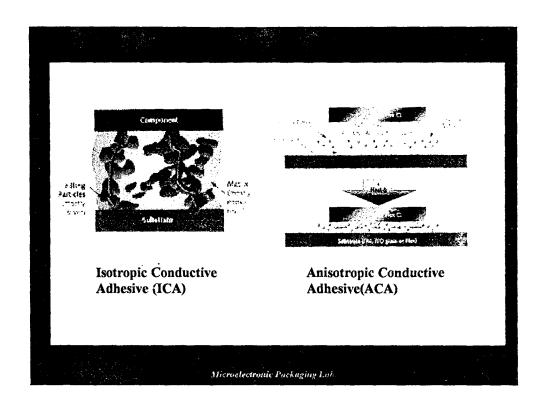

### 2. Non-Solder bumps – ICAs or ACAs

- Gold bumps

- Au stud bumps

- Electroless Ni/Au plated bumps

- Electrical interconnection medium such as ICAs and ACAs needed

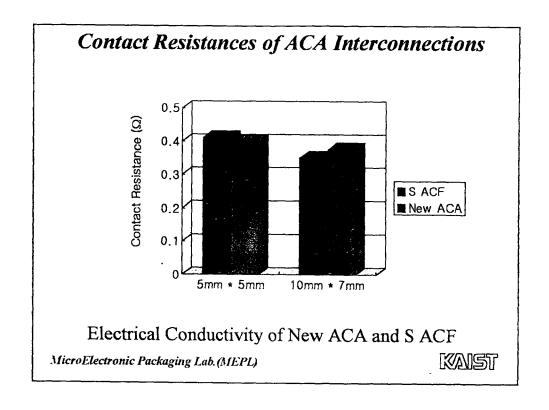

# ACFs/ACAs Materials

### 1. Conductive Particles

- Particle Types: metal particles (Ni. Ni/Au, solder) or metal coated polymer particles

- Number, Diameter, Hardness, Conductivity

- ACFs/ACAs Design Parameters optimization

- Experimental Verification

## 2. Polymer Resin

- Polymer types:

- thermosetting(epoxy) & thermoplastics

- Curing kinetics of epoxy resin

- · Curing agents and amount

Ğ

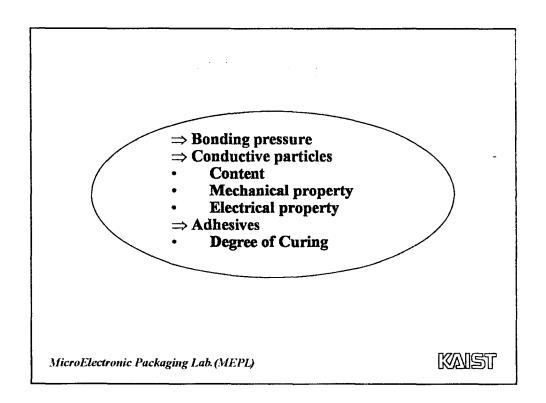

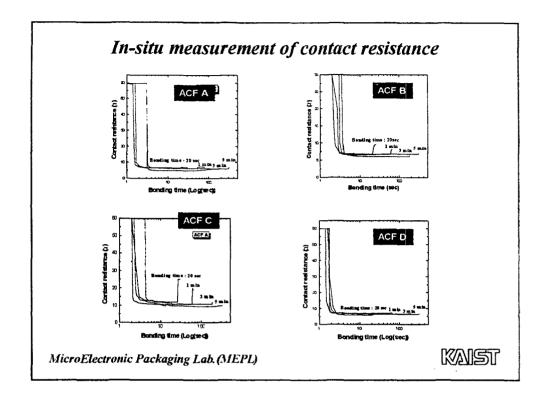

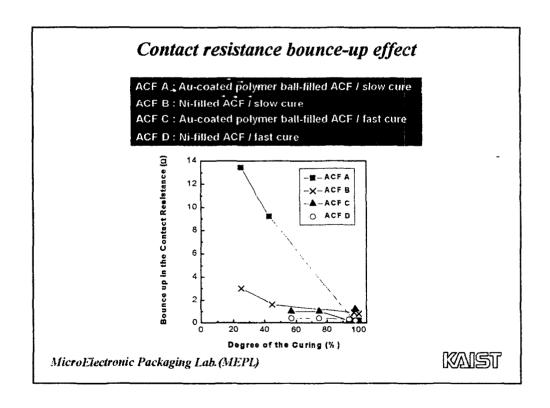

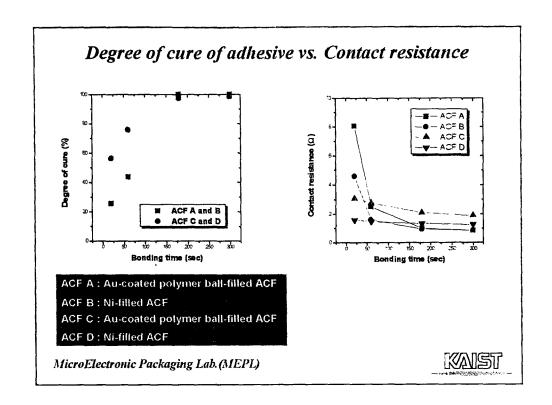

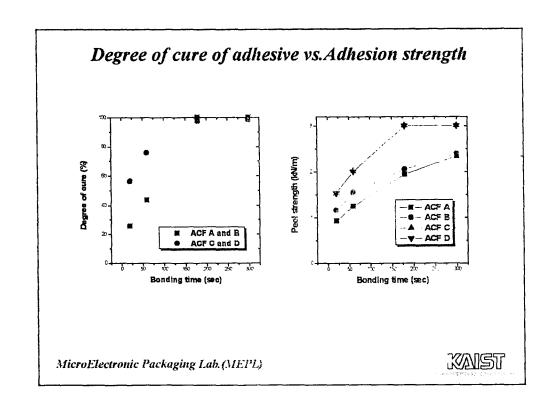

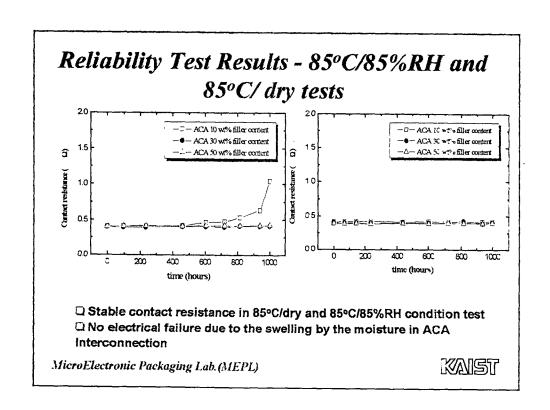

## Experimental Procedure

### The evaluation of ACF interconncetion characteristics

(1) Conductive filler Ni-filled ACF materials Au-coated polymer-filled ACF

Ni-filled ACF

(2) Content of fillers 1, 2, 3, 4, 5, 6, 8 wt%

(3) Bonding variable Bonding pressure

1.5, 2, 3, 4, 5 kgf/cm<sup>2</sup>

### Measurement of Contact resistance

MicroElectronic Packaging Lab. (MEPL)

KAUST

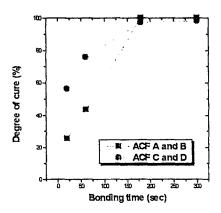

### Cure kinetics of epoxy resin

MicroElectronic Packaging Lab.(MEPL)

á

# **Summary**

- ▶ Performance, reliability, form factor drive flip chip use

- ▶ BGAs and CSPs will provide stepping stone to FC DCA

- ▶ Growing vendor infrastructure

- Low cost, high density organic substrates

- New generations of fluxes and underfills

- ▶ Adhesives flip chip technology as a low cost flip chip alternatives

- ▶ Low cost Au stud or Electroless Ni bumps

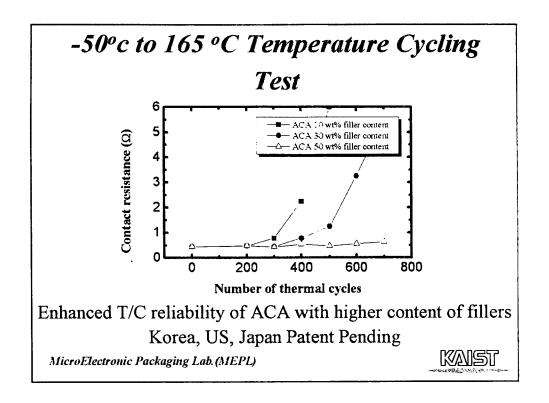

- ▶ Reliable thermal cycling and electrical performance

## Flip Chip Interconnection method applied to small camera module

\*Masao Segawa, \*Michiko Ono, \*Jun Karasawa, \*\*Kenji Hirohata

\*\*\*Makoto Aoki, Akihiro Ohashi, Tomoaki Sasaki, \*\*\*\*Yasukazu Kishimoto

\*Manufacturing Engineering Research Center, Toshiba Corp.

\*\*Research & Development Center, Toshiba Corp.

\*\*\*Fukaya Visual Products Works, Toshiba Corp.

\*\*\*New Product Development Center, Toshiba Chemical Corp.

\*33, ShinIsogo-cho, Isogo-ku, Yokohama, Japan 235-0017

#### **Abstract**

A small camera module fabricated by including bare chip bonding methods is utilized to realize advanced mobile devices. One of the driving forces is the TOG (Tape On Glass) bonding method, which reduces the packaging size of the image sensor chip. The TOG module is a new thinner and smaller image sensor module, using flip chip interconnection method with the ACP (Anisotropic Conductive Paste). The TOG production process was established by determining the optimum bonding conditions for both optical glass bonding and image sensor chip bonding to the flexible PCB. The bonding conditions, including sufficient bonding margins, were studied. Another bonding method is the flip chip bonding method for DSP (Digital Signal Processor) chip. A new ACP was developed to enable the short resin curing time of 10 sec. The bonding mechanism of the resin curing method was evaluated using FEM analysis. By using these flip chip bonding techniques, small camera module was realized.

#### Introduction

Many portable electronic products have been developed and put on the market, with the evolution of digital information data compression technology and high-quantity memory storage devices. The market for small cameras as image storage devices has been rapidly increasing with the improvement of picture quality and the advantage of the easy picture processing method. Toshiba developed the world's smallest and lightest Ø 7mm camera using a 400k pixel CCD chip for industrial application in 1994, as shown in Fig.1 [1]-[6]. Also, a small digital still camera was put on the market in July 1997, as shown in. Fig. 2., A 330 k pixel CMOS image sensor chip is used, as an image sensor, to realize low power consumption and reduction of the image processing circuit. The size of the camera is  $105(W) \times 55(H) \times 20 \text{mm}(D)$ , and it weighs only 130g [7][8].

The driving force for the size reduction of the camera was to develop a small image sensor module [1]-[7]. In order to meet this demand, the adoption of a bare chip bonding technique is the first requirement. Furthermore, some restrictions should be considered to fabricate the module. First, a low bonding temperature of under 200°C must be observed to prevent the heat damage of the color filters formed on the CMOS chip. Second, a cavity structure must also be formed to maintain the effect of the microlens on the chip. To resolve these restrictions and to realize a simple production process, the authors have developed a new image sensor module, which is fabricated by bare chip bonding and unique interconnection methods.

Furthermore, to reduce the module size, the flip chip bonding method for DSP (Digital Signal Processor) chip was developed. The new camera module was put on the market in 1999, as shown in Fig. 3. A new ACP was developed to enable the short resin curing time of 10 sec. The bonding mechanism for the resin curing method was evaluated by FEM analysis[9].

Fig.1 External appearance of \$\phi7mm \text{microcamera}\$

Fig.2 External appearance of the digital still camera

Fig.3 External appearance of the picture-mail Communication device

#### Image sensor fabrication method

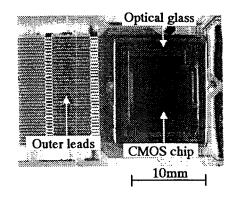

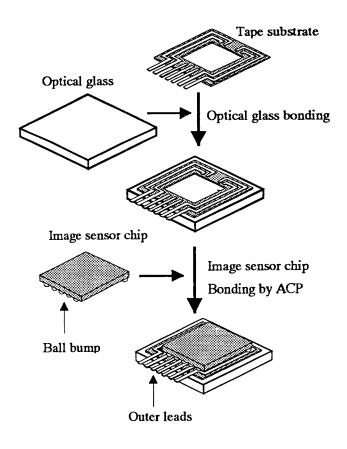

The TOG module has some unique features which have never been obtained in the conventional package by the wire bonding method. The typical external appearance of the TOG module is shown in Fig. 4. The size of the module is  $8.8 \times 10.3 \times 11.65$ mm, which is almost as small as the CMOS bare chip. The module has a simple packaging structure by combining with a CMOS chip, optical glass, and flexible PCB substrate.

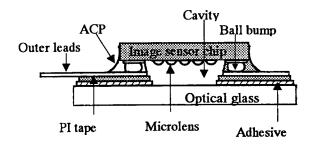

The TOG module, in which the fine pitch outer leads are bent and directly connected to the main printed circuit board, contributes significantly to the reduction of the total thickness of the camera. A cross sectional image of the TOG module is shown in Fig. 5. Here, some critical binding conditions, which are particularly limited for image sensor chip bonding, unlike for other typical bare chip bonding, should be taken into account. Initially, the CMOS chip cannot withstand high temperatures, since plastic color filters and the microlens are formed on the image pixels of the chip. The heat prevention limit is around 150°C. Therefore, low-temperature bonding is required. Next, a cavity structure should also be realized to maintain the effect of the microlens which is formed on the top surface of the chip. In this case, thermal stress will be generated in the bonding portions, since the air present in the cavity will expand and contract in accordance with temperature change.

The production process of the TOG module is illustrated in Fig. 6. First, the optical glass is directly attached to the flexible PCB tape substrate by adhesive. The optical glass can be easily attached to the flexible PCB tape with a highly accurate optical verticality of under 10 µm. Gold ball bumps of Ø90µm and 30µm height are preformed on the aluminum electrodes of the image sensor chip by the wire bonding method. Then, the ACP is coated on the electrodes of the flexible PCB. In the next process, the image sensor chip can be directly bonded to the electrodes of the flexible PCB using a highly accurate bonding machine. Heat press bonding is applied to cure the ACP so that the desired bond characteristics can be obtained. Subsequently, by curing the ACP under the appropriate bonding conditions, complete sealing and electrical contacts between the image sensor chip and the flexible PCB can be simultaneously obtained.

### Studies on the TOG production process

### 1. Bonding process of the flexible PCB and optical glass

For the case of the bonding process of the flexible PCB and optical glass, the optimum adhesion conditions were studied. In order to reduce the adhesion time, UV curing-type acryl resin or epoxy resin by heat press curing type is used. To obtain sufficient adhesion strength, the authors evaluated the effect of the roughness of the tape. A practical peeling strength of over 100gf/mm, which can withstand the bending process, and high reliability were obtained.

2. Bonding process of the image sensor chip and flexible PCB Simple and highly reliable bonding can be obtained in the TOG module construction by applying the unique ACP bonding technique. ACP consists of small conductive

Fig.4 External appearance of the TOG module

Fig.5 Cross section image of the TOG module

Fig.6 TOG module production process

particles of approximately  $\emptyset 5 \mu m$ , which are dispersed in a high-speed curing-type epoxy resin. The ACP curing agent was improved to realize a 50% curing time reduction to 10 sec at 170°C, and to prolong the pot life of the ACP to more than three months[7]. Also, some gradients were effectively added to the ACP in order to prevent ACP bleeding towards the image area of the chip, which results in image defects.

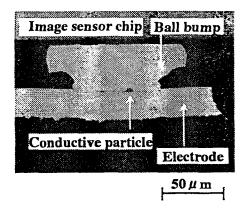

With the appropriate heat press bonding, the specified electrical contacts can be obtained by the conductive particles, which are sandwiched between the gold ball bumps on the chip and the electrodes on the flexible PCB.

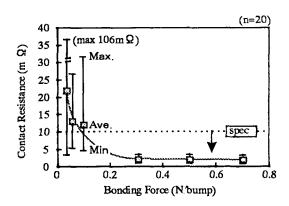

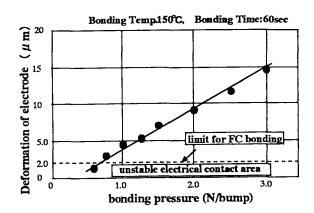

The main parameters of the anisotropic conductive bonding are the bonding temperature, bonding force, and bonding time. Among these parameters, the bonding temperature and time are significantly dependent on each other[4]-[7]. As the temperature applied to the ACP rises, the curing time becomes short exponentially. Although the bonding time can be reduced in 5 sec as the bonding temperature rises up to 180°C, the bonding temperature should be set under the heat prevention limit of the sensor chip. The optimum bonding conditions were evaluated. Figure 7 shows the relationship between the bonding pressure and the contact resistance. At a low bonding pressure of under 0.1N/bump, the contact resistance is relatively high and unstable with large resistivity variation. On the other hand, at a bonding pressure of above 0.3N/bump, the contact resistance is stable and lower than  $10 \text{m}\Omega$ .

At the constant bonding temperature of 170°C under conditions of a bonding force of over 1.5kgf/chip and a bonding time of over 10 sec, electrical contact and sufficient bonding strength can be obtained. Figure 8 shows a cross-sectional view of the enlarged bonding portion between the image sensor chip and the flexible PCB. The gold ball bump sufficiently contacts to the electrode, not only due to the conductive particles between the gold ball bump and the electrode, but also due to the contact between other major surfaces of the gold ball bump and the electrodes. Reliability tests were executed for the TOG module, as summarized in Table 1. The TOG module exhibits a high reliability in the main reliability tests such as the thermal cycle test and the high temperature and humidity storage test.

#### Studies on the flip chip bonding of the DSP chip

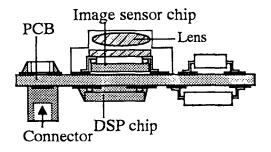

Figure 9 shows a cross section of the camera module applied to mobile communication device shown in Fig. 3. The module is fabricated by two bare chip bonding methods for both of the CMOS image sensor and the DSP chip. As shown in Fig. 9, on the top side of the four-layered glass epoxy substrate, TOG module of image sensor of 110K-pixels is mounted. On the bottom side, DSP chip  $(6.0 \times 6.0 \times 10.45$  mm, 80pins) is mounted by the new ACP. Figure 10 shows the external appearance of the camera module. Simple and highly reliable flip chip bonding method was developed. The new ACP consists of small conductive particles of about  $\emptyset3$  µm, which are dispersed in a high-speed curing-type epoxy resin. The new ACP has the curing time of 10 sec, which is

Fig.7 Relationship between the bonding pressure and contact resistance

Fig.8 Cross section of bonding portion

Table.1 Reliability of the TOG module

| Test items                      | Conditions                                              | Results |

|---------------------------------|---------------------------------------------------------|---------|

| Thermal cycle test              | -40 ~ +110°C /30 min<br>2000cycles, n=20                | Passed  |

| High temp. and humidity storage | 60°C, 90%RH<br>3000h, n=20                              | Passed  |

| High temp. and humid. operation | 40°C 90% RH, 3.3V<br>72h, n=5                           | Passed  |

| Bubble leak test                | Dipping in Fluorinert <sup>1M</sup> of 120°C/60sec, n=5 | Passed  |

| Dew occurrence test             | 60°C,90% RH<br>3000h, n=10                              | Passed  |

Fig.9 Cross section of the camera module

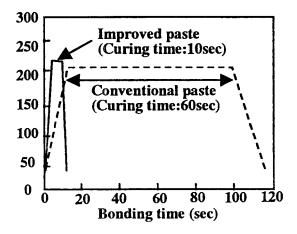

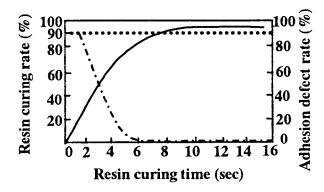

one-sixth of the conventional ACP. The relationship between the resin reaction rate time and the bonding time is shown in Fig. 11. If the bonding time exceeds 6 sec, a high resin curing rate of over 90% can be obtained. Moreover, sufficient adhesion strength between the chip, resin and substrate can be confirmed in the case that the bonding time is over 10 sec, as shown in Fig. 12.

Next, bonding mechanism was studied. Figure shows that the deformation value increases in proportion to the bonding pressure. From the above test result, if the deformation is kept over  $2.0\mu m$ , then the required bonding pressure should be set to over 0.8N/bump.

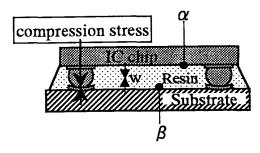

Considering the above test results, we estimated the bonding stress of the ACP bonding method. As illustrated in Fig. 14, bonding stress is generated from the following relationship.

$\alpha$ : adhesion strength between chip and resin

$\beta$ : adhesion strength between substrate and resin

w: resin shrinkage stress after curing

p: resin stress by temperature change

where  $\alpha \beta > w > p$ .

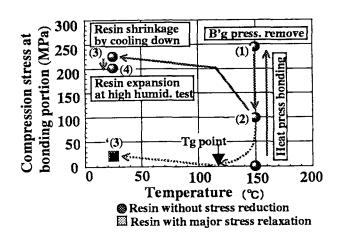

Figure shows the FEM analysis result and stress change following the bonding procedure. At first, bare chip is bonded by applying heat and pressure in step (1). Maximum compression stress generates at the bonding portion. Then, the bonding pressure is removed and the stress was mainly reduced in step (2). Next, the bonding stress is increased as the temperature decreased to the room temperature (RT) after the bonding in step (3). In this FEM analysis, the initial compression stress is approximately 230MPa in step (3). The initial bonding margin can be reduced in a reliability test such as the high temperature and humidity storage test. If the module is tested in high temperature and humidity storage (60°C, 90%, 1000h), the compression stress will be reduced by 10%. Furthermore, if the resin had its own stress relaxation property during the resin curing process, it was unable to obtain sufficient bonding stress, as shown in step '(3). The FEM data was compared by the deformation value as shown in Fig. 13. Good coincidence between the data was verified.

#### Conclusion

- The TOG (Tape On Glass) bonding method realizes a thin and small image sensor package. The production processes of image sensor chip bonding to the flexible PCB by ACP were determined with enough bonding margin and high reliability.

- 2. For the flip chip bonding method for DSP (Digital Signal Processor) chip, a new ACP was developed to enable the short resin curing time of 10 sec. The bonding mechanism for the resin curing method was evaluated by FEM analysis.

- Small camera applied to mobile device application was realized by using these advanced flip chip bonding methods.

Top side (CMOS chip is mounted)

Bottom side (DSP chip is mounted)

Fig.10 External appearance of the camera module

Fig.11 Comparison of ACP curing profile

Fig.12 Comparison of ACP curing profile

#### References

- 1. Y. Kondoh and M. Saito, "A New CCD Module Using The Chip On Glass (COG) Technique" in Proc. ISHM 1990, pp. 487-494.

- 2. T. Suzuki, H. Mimura, K. Tamura, and M. Hirano, "Micro Head TV Camera", National Technical Report, Vol.41, No.2, pp.225-232, Apr. 1995.

- 3. M.Segawa, M. Kimura, K. Ooi, and S. Sugi, "A Micro Miniaturized CCD Color Camera Utilizing A Newly Developed CCD Packaging Technique", IEEE Trans. ICCE, vol.41, No.3, pp.946-953, Aug. 1995.

- M. Segawa, M. Kimura, K. Ooi, and S. Sugi, "A New CCD Package Utilizing The TOG (TAB On Glass) Bonding Technique", in Proc. IMC, 1996, pp.389-394.

- A. Ohashi, K. Someno, and M. Segawa, "IK-SM40 Super Micro Camera", Toshiba Review, vol.50, No.11, pp.859-862, 1995.

- M. Ono, M. Segawa, S. Sugi, M. Kimura, K. Ooi, and Y. Kishimoto, "An Ultra Small Image Sensor Module For Ø4mm Micro Camera", in Proc. MES, 1997, pp.29-32.

- 7. J. Karasawa, T. Terui, Y. Saito, M. Arakawa, S. Sugi, "A Small Multichip Camera Module Utilizing ACP Interconnection Method", in Proc. IMC, 1999, pp.414-419.

- M. Segawa, M. Ono, S. Musha, Y. Kishimoto, A. Ohashi, "A CMOS Image Sensor For A Digital Still Camera Utilizing The TOG (TAB On Glass) Bonding", in IEEE transaction, vol.22, No.2, pp.160-165, May 1999.

- 9. K.Hirohata, "Bonding Margin Evaluation of Flip Chip Bonding Method" in Proc. of the 14th JIEP Annual Meeting March, 2000, pp.101-102.

Fig.13 Deformation of electrode dependent on bonding pressure

Fig.14 Parameters for flip chip bonding method

Fig.15 Bonding stress simulation for flip chip bonding sequence