## 멀티겐벨 인버터 및 컨버터를 위한 새로운 저손실 스너버

김인동, 노의철 부경대학교 전기공학과

# A New Generalized Undeland Snubber Circuit for Multilevel Inverter and Converter

In-Dong Kim and Eui-Cheol Nho

Dept. of Electrical Engineering, Pukyong National University

Abstract - This paper proposes a new snubber circuit for multilevel inverter and converter. The snubber circuit makes use of Undeland snubber as basic snubber unit and can be regarded as a generalized Undeland snubber. The proposed snubber keeps such good features as fewer number of components, improved efficiency due to low loss snubber, capability of clamping overvoltage across main switching devices, and no unbalance problem of blocking voltage. Furthermore, the proposed concept of constructing a snubber circuit for multilevel inverter and converter can apply to any kind of basic snubber unit such as Holtz nondissipative McMurray efficient Lauritzen lossless snubber, etc which have been utilized for two-level inverter.

#### 1. Introduction

Recently the multilevel inverter and converter have drawn tremendous interest for high voltage and high power applications (1)-(7). The general structure of the multilevel and converter is to sinusoidal voltage waveforms from levels of voltages typically obtained from capacitor voltage sources. As the number of increase. the synthesized waveform adds more steps, producing staircase waveform which approaches the sinusoidal wave with minimum harmonic distortion. More levels also mean that higher DC link voltage than voltage rating of device itsef can be handled by series device without device voltage sharing problem and without the use of bulky and heavy transformer for multiple connections.

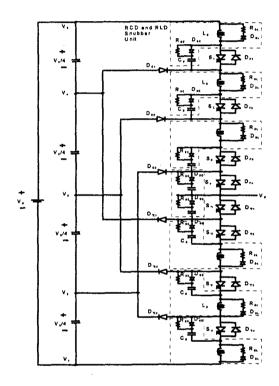

Until now, for multilevel inverter and converter, conventional RCD and RLD snubber as turn-off snubber and turn-on snubber. respectively, have been used widely and exclusively as shown in Fig. 1 because it is easy to apply to multilevel inverter and converter (6)-(7). But this kind of snubbers need separate snubber circuit unit for each GTO which are composed of turn-off capacitors. turn-on inductors, resistors and diodes. Thus the total number of snubber components become considerably high and complex, thus resulting highly costly multilevel inverter converter. And since the large amount of snubber energy is fully dissipated in snubber

Fig. 1 Five-level inverter with conventional RCD/RLD snubber(within the dotted line).

resistor, system power loss can be very high, which causes system efficiency to become very low. Furthermore, during turn-off process, the overvoltage of GTO can be very high, usually about 1.8 times higher than DC link voltage because there is only one small turn-off capacitor for each GTO to absorb the stored inductor energy. In addition, unbalance problem overvoltage, which results multilevel combination of structure and RCD/RLD snubbers, makes voltage stresses of the switching devices worse[7].

To overcome the above-mentioned disadvantage of RCD/RLD snubber for multilevel inverter and converter, a new snubber topology suitable for multilevel inverter and converter are proposed. The proposed snubber utilizes Undeland snubber as basic snubber unit and can be regareded as a generalized Undeland snubber for multilevel

structure converter. Its good features include fewer number of component, improved efficiency due to low loss snubber, capability of clamping overvoltage across switching main device and no unbalance problem of blocking voltage. This paper also explains in detail how to construct a snubber circuit for multilevel inverter and converter and simulational results of the new converter are included.

## 2. The Proposed Snubber for Multilevel Inverter and Converter

An m-level multilevel inverter typically consists of m-1 capacitors on the DC bus and produces m-levels of the phase voltage. Fig. 2(a) shows one pole of five-level inverter in which the DC bus consists of four capacitors,  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ . For a DC bus voltage  $V_S$ , the voltage across each capacitor is  $V_S/4$  and each device stress will be limited to one capacitor voltage level.  $V_S/4$ , through clamping diodes. Table 1 lists the voltage levels and their corresponding states. State condition 1 means the switch is on, and 0 is off. There exist four complementary switch pairs in each phase The complementary switch pair is defined

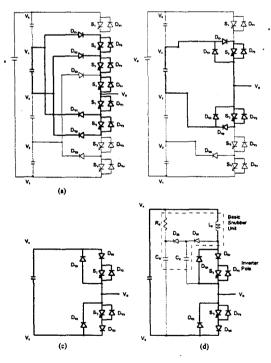

Fig. 2 Derivation of the proposed snubber for multilevel inverter (a)the operating part of circuit (thick line) during level changes between V4 and V3, (b) Redrawn circuit of (a), (c)Equivalent two-level inverter during level changes between V4 and V3, (d)Equivalent two-level inverter with a basic snubber unit.

such that turning on one of the pair switches excludes the other from being turned on. In inverter, the four five-level case of  $(S_1, S_1), (S_2, S_2),$ complementary pairs are  $(S_3, S_3)$ , and  $(S_4, S_4)$ which, respectively, correspond to each level change, that is, between  $V_5$  and  $V_4$ ,  $V_4$  and  $V_3$ ,  $V_3$  and  $V_2$ , and  $V_2$  and  $V_1$ . Notice that the level changes occur only between adjacent levels. When investigating all level changes, we can find the operating part of circuit during each level change to converge to equivalent two level inverter which is composed of complementary pair switches and corresponding clamping diodes. For example, as shown in Fig. 2. consider level changes between  $V_3$ and  $V_4$ . The corresponding complementary pair is  $(S_2, S_2)$ . If  $S_2$  is on and  $S_2$  is off, output level is  $V_4$ . Convesely, If  $S_2$  is off and  $S_2$  is on, output level is  $V_3$ . During these level changes the operating components of five-level inverter can be drawn with thick line as shown in Fig.

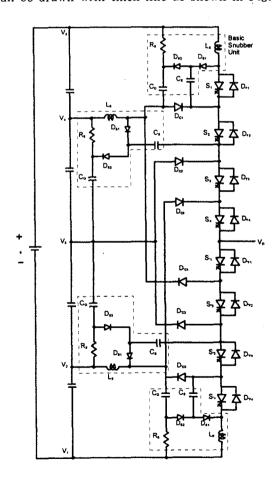

Fig. 3 Five-level inverter with the proposed snubber.

2(a). The thick-lined part of operating circuit can be transformed into Fig. 2(b) and can also be redrawn as Fig. 2(c) since switches  $S_3$ ,  $S_4$ . and  $S_1$  are always turned on irrespective of on/off condition of  $S_2$  and  $S_2$ . Fig. 2 (c) shows that the operating part of circuit is equivalent to the conventional two-level voltage source inverter. It follows that for the equivalent two-level inverter related to switching devices  $(S_2, S_2)$ , the basic snubber unit which have been used in two-level inverter can be applied as shown in Fig. 2(d). In the same way, all the equivalent two-level inverter corresponding level change, that is, complementary pair in multilevel inverter can be derived, and the same basic snubber units can apply to them. So, we can obtain five-level inverter equipped with a snubber circuit as shown in Fig. 3. When using the same principle, we can get the snubber circuits for 3-level, 4-level. Furthermore, a generalized snubber for any multilevel inverter and converter can be achieved. The generalized snubber has the same good features as the basic snubber unit. In this paper since we use the Undelnand snubber(8) as the basic snubber unit, the characteristics of the generalized snubber are such as fewer number component, improved efficiency due to low loss snubber, capability of clamping overvoltage switching main device and arrangements and mounting of snubber circuit. Furthermore thanks to the snubber structure. the generalized snubber has no unbanlance problem of overvoltage unlike RCD/RLD snubber, thus resulting in equal voltage stress to all main switching devices except clamping diodes.

## 3. Conclusion

This paper proposes a new snubber circuit for multilevel inverter and converter. The snubber circuit makes use of Undeland snubber as basic snubber unit and can be regarded as a generalized Undeland snubber. The proposed snubber keeps such good features as fewer number of component, improved efficiency due to low loss snubber, capability of clamping overvoltage across switching main device and no unbalance problem of blocking voltage. Furthermore, the proposed concept constructing a snubber circuit for multilevel inverter and converter can apply to any kind of basic snubber unit such as Holtz nondissipative snubber(9), McMurray efficient snubber(10), Lauritzen nondissipative snubber(11), etc which can be utilized for two-level inverter.

### References

- Nam S. Choi, Jung G. Cho and Gyu H. Cho, "A General Circuit Topology of Multilevel Inverter," IEEE PESC, pp96-103, 1991.

- [2] C. Hochgraf, R. Lasseter, D. Divan and T. A. Lipo, "Comparison of Multilevel Inverter for Static Var Compensation," IEEE IAS Annual Meeting Conf. Record, pp. 921-928, 1994.

- (3) J.-S. Lai and F. Z. Peng, "Multilevel Converters-A New Breed Power Converters," IEEE IAS Annual Meeting Conf. Record, pp. 2348-2356, 1995.

- [4] Nam S. Choi, Cuk C. Cho and Gyu H. Cho. "Modeling and Analysis of a Static Var Compensator using Multilevel Voltage Source Inverter," IEEE IAS Annual Meeting Conf. Record, pp. 356-365, 1993.

- [5] F. Z. Peng, J.-S. Lai, J. Mckeever and J. VanCoevering, "A Multilevel Voltage-Source Inverter with Seperate DC source for Static Var Generation." IEEE IAS Annual Meeting Conf. Record, pp. 2541-2548, 1995.

- [6] G. Sinha, C. Hochgraf, R.H. Lasseter, D.M. Divan T.A. Lipo, "Fault Protection in a Multilevel Inverter Implementation of a Static Condenser," IEEE IAS Annual Meeting Conf. Record, pp. 2557-2564, 1995.

- [7] B. S. Suh, D. S. Hyun and H. K. Choi, "A Circuit Design for Clamping an Overvoltage in Three-level GTO Inverters," IEEE IECON, pp651-656, 1994.

- [8] T. Undeland, F. Jenset, A. Steinbakk, T. Rogne and H. Hernes, "A Snubber Configuration for Both Power Transistor and GTO PWM Inverters," IEEE PESC, pp42-53, 1984.

- (9) J. Holtz, S. Salama, and K.H. Werner, "A Nondissipative Snubber Circuit for High-Power GTO Inverters," IEEE Trans. Ind. Appli., vol. 25, No. 4, pp. 620-626, July/Aug. 1989.

- 25. No. 4, pp. 620-626, July/Aug. 1989.

(10) W. McMurrayA, "Efficient Snubbers for Voltage-Source GTO Inverters," IEEE Trans. Pow. Elec., vol. PE-2, No. 3, pp. 264-272, July 1987.

- [11] P.O. Lauritzen, and H.A. Smith, "A Nondissipative Snubber Effective over a Wide Range of Operating Conditions," IEEE PESC, pp345-454, 1983.

Table 1

Five-level inverter voltage levels and corresponding switch states

| Output            | Switch State |    |                |                |    |                |                |                |

|-------------------|--------------|----|----------------|----------------|----|----------------|----------------|----------------|

| $v_{o}$           | $S_1$        | S2 | S <sub>3</sub> | S <sub>4</sub> | Sı | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> |

| $V_5=V_S$         | 1            | 1  | 1              | 1              | 0  | 0_             | 0              | 0              |

| $V_4 = 3V_S/4$    | 0            | 1  | 1              | 1              | 1  | 0_             | 0              | 0              |

| $V_3=2V_S/4$      | 0            | 0  | 1              | 1              | 1  | 1_             | 0              | 0              |

| $V_2 = V_5/4$     | 0            | 0  | 0              | 1              | 1  | 1              | 1              | 0              |

| V <sub>1</sub> =0 | 0            | 0  | 0              | 0              | 1  | 1              | 1              | 1              |

(1: On, 0: Off)