## A PSpice Modeling of PFC Circuit Using Soft-Switched Boost Converter

H.S. Mok, G.H Choe,

S.E. Jeong.

J.Y. Choi.

Kon-Kuk Univ.

Hanyang Univ.

Korea Institute of

Science and Technology.

#### **Abstract**

Single-phase and three-phase AC to DC power converters are becoming frequently used for high voltage/high power applications such telecommunications. They often require input/output transformer isolation for safety, a unity input power factor for minimum reactive power, free input harmonic currents fed back to the AC power distribution system and, finally, high efficiency and high power density for minimum weight and volume. The proposed boost converter for power factor correction (PFC) provides a unity input power factor, low harmonic distortion and high efficiency along with reduced volume and weight. Single-phase 220VAC input/380VDC IKW output prototype is constructed and experimental results will be verified with those of *PSpice* simulation.

## I. Introduction

In most power electronics applications, the power input is in the form of 60Hz sine wave ac voltage provided by the electric utility company, which is converted desired dc output voltage. Increasingly, the recent trend is to use diode rectifiers at the first converting stage to convert the ac input to dc with large capacitor connected as a filter on the dc side to reduce dc side ripple. However, this large size filter capacitor gets charged to the peak of the ac input voltage drawing highly distorted current from the utility. But recently, harmonic pollution of the utility becomes big issues and strict standards and guidelines imposes the amount of current distortion allowed into the utility, and simple diode rectifiers connected with large input capacitors

are becoming restricted. Proper circuits for single phase and three phase inputs to achieve a nearly sinusoidal current rectification at a unity power factor should be provided for a majority power electronics applications such as switch-mode power supplies. The proposed boost converter provides a unity input power factor, low harmonic distortion and high efficiency along with reduced volume and weight. Single-phase 220VAC input/380VDC 1KW output prototype is constructed and experimental results will be verified with those of *PSpice* simulation.

# II. Operation Mode of ZVT-PWM Boost Converter

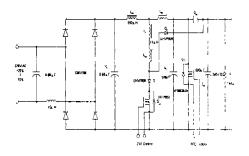

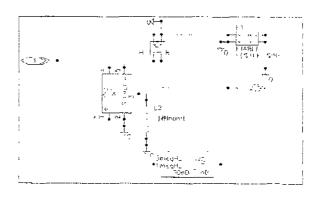

The implementation of the power factor correction (PFC) circuit with DC output rectification has been popular recently and an attempt was made combining both PFC and zero-voltage-transition (ZVT) for better efficiency and reduced harmonic contents of the input currents. For an improved power density and higher switching frequency. ZVT technique was applied to boost converter shown in

Fig. 1. 100KHz 1KW PFC Ckt.

Using Boost ZVT PWM Converter

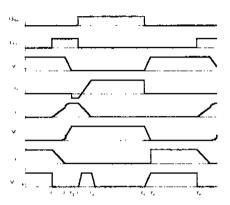

Fig. 1. This topology utilize the parasitic capacitance of the MOSFET switches and the necessary amount of inductance for resonant switching with ZVT, and its expected key voltage and current waveforms are shown in Fig. 2.

Fig. 2. Expected Key Waveforms of the ZVT-PWM Boost Converter

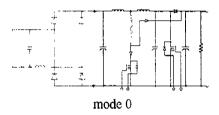

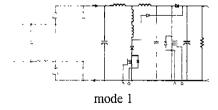

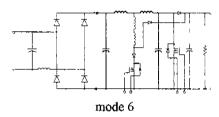

There are seven operating modes within one switching cycle as shown in Fig. 3 and each operating mode is summarized as follows:

Fig. 3. Operating Modes of the ZVT-PWM Boost Converter

- mode 0 (prior to T<sub>0</sub>): The main diode D<sub>m</sub> is only conducting and supplying energy to the load from rectified ac source. Remaining all the other switches and diodes are turned off and L<sub>S2</sub> has been saturated.

- mode 1 (T<sub>0</sub> T<sub>1</sub>): Before turning on main switch S<sub>m</sub>, the auxiliary switch S<sub>a</sub> starts to turn on. L<sub>r</sub> current i<sub>Lr</sub> linearly ramps up with the slope of Eqn. (1) before L<sub>S1</sub> saturates and with the slope of Eqn. (2) after L<sub>S1</sub> saturates.

$$\frac{di_r}{dt} = \frac{V_{IN}}{L_r + L_{sI}} \tag{1}$$

$$\frac{di_r}{dt} = \frac{V_{lN}}{L_r} \tag{2}$$

Correspondingly,  $D_m$  current  $i_{Dm}$  is decreasing according to the above equations. However, when  $L_{S2}$  is out of saturation,  $i_{Dm}$  decreases to zero as following rate:

$$\frac{di_r}{dt} = \frac{V_{1N}}{L_r + L_{s2}} \tag{3}$$

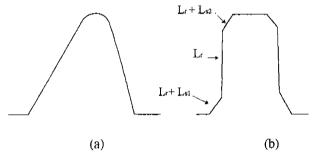

The resulting shape of  $L_r$  current  $i_{Lr}$  and  $D_m$  current  $i_{Dm}$  are shown in Fig. 4., which reduces unnecessary duty cycle loss in the process of achieving zero-voltage switching for main switch  $S_m$ . The required time is simplified as follows neglecting the effect of two saturable inductors  $L_{S1}$  and  $L_{S2}$ :

$$t_{0l} = \frac{I_L}{V_{0.}}$$

$$L_r$$

(4)

Fig. 4. Inductor Current Waveform (a) without and (b) with two saturable inductors  $L_{\rm S1}$  and  $L_{\rm S2}$

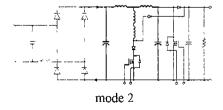

• mode 2 (T<sub>1</sub>- T<sub>2</sub>): When i<sub>Lr</sub> reaches I<sub>L</sub> at T<sub>1</sub>, D<sub>m</sub> turns off with zero-voltage and zero-current switching and C<sub>r</sub> is discharged until the resonance brings its voltage to zero at T<sub>2</sub>. and its anti-parallel diode of S<sub>m</sub> starts to conduct. The minimum required interval for this period is a quarter of whole resonant cycle (T) as given:

$$t_{12} = \frac{T}{4} = \frac{\pi}{2} \sqrt{L_r C_r} \tag{5}$$

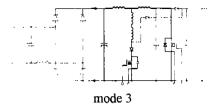

• mode 3 (T<sub>2</sub>- T<sub>3</sub>): The anti-parallel diode of S<sub>m</sub> starts to conduct and the gate signal is applied to main switch S<sub>m</sub> at zero-voltage. The minimum time delay between S<sub>a</sub> and S<sub>m</sub> gate-drive turn-on signals is determined as following:

$$T_D \ge t_{01} + t_{12} = \frac{I_L}{V_{0/L_r}} + \frac{\pi}{2} \sqrt{L_r C_r}$$

(6)

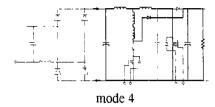

- mode 4 (T<sub>3</sub>- T<sub>4</sub>): The auxiliary switch S<sub>a</sub> turns off at T<sub>3</sub>, and S<sub>m</sub> starts to conduct. The energy of L<sub>r</sub> is transferred to the load through the auxiliary diode D<sub>2</sub>, then, i<sub>Lr</sub> decays to zero. The fast recovery diode D<sub>1</sub> is placed to prevent the conduction of S<sub>a</sub> body diode due to the resonance between L<sub>r</sub> and S<sub>a</sub> output capacitance after T<sub>4</sub>.

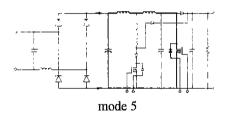

- mode 5 (T<sub>4</sub>- T<sub>5</sub>): The auxiliary diode D<sub>2</sub> turns off at zero-current switching while its reverse recovery current is limited by the saturable inductor L<sub>s1</sub> and the main switch S<sub>m</sub> fully conducts. Then, finally, the whole procedure of zero-voltage switching for main switch S<sub>m</sub> is finished.

- mode 6 ( $T_5$   $T_6$ ): At  $T_5$ , the main switch  $S_m$  turns off at zero voltage in charging the resonant capacitor  $C_r$  with the rate of Eqn.(7):

$$\frac{dV_{Sm}}{dt} = \frac{I_L}{C_-} \tag{7}$$

# III. Implementation of ZVT-PWM Boost Converter using PSpice

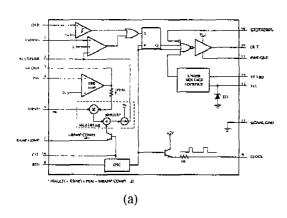

A. PFC Controller Using Peak-Current Mode Control

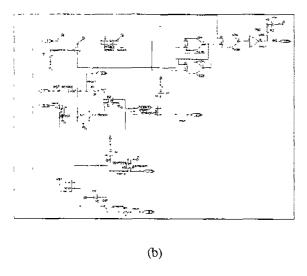

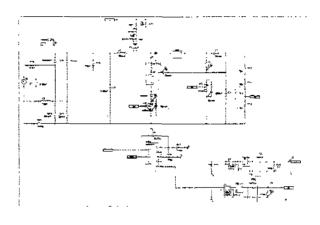

The ML4812 is designed to optimally facilitate a "boost' type power factor correction system. In a typical application, the ML4812 functions as a current regulator. The current which is necessary to terminate the cycle is a product of the sinusoidal line voltage times the output of the error amplifier which is regulating the output DC voltage. In order to provide stable operation in case duty cycle exceeds 50%, ramp compensation is programmable with external resistor. Figure 5 (a) and (b) show a block diagram of ML4812 and its implementation using Pspice.

Fig. 5. (a) Block diagram of ML4812 (b) its implementation using *Pspice*

#### B. Saturable Inductor

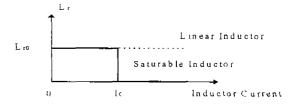

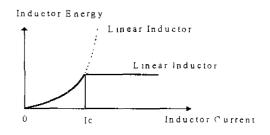

Saturable inductors are used in the proposed PFC system, which is enable to shorten the conduction time of auxiliary switch S<sub>a</sub>. Figure 6 shows the characteristics of an ideal saturable inductor and a linear inductor below and Fig. 7 is a detailed implementation of the ideal saturable inductor.

Fig. 6. Characteristics of an ideal saturable inductor and a linear inductor

Fig. 7. a detailed implementation of the ideal saturable inductor

#### VI. Conclusions

At present, the cost, slightly higher power losses, and complexity of active current shaping have prevented their widespread usage. However, this may change in the future because of increased device integration leading to lower semiconductor cost, a strict enforcement of harmonic standards, and some of the advantages mentioned above. Another factor in favor of the active line-current shaping is as follows: in power supplies to computers, a sinusoidal line current is important to avoid the added kVA rating and, hence the increased cost of the UPSs, and standby diesel generators, which often supply computer systems. Therefore, ICs and other components suitable for these applications have become available, which will lower the cost of development and the components of the PFC circuit.

This paper addresses the analysis and design of three single-phase ac-to-dc converter which draws high quality input current waveforms from the ac source. Compared with a hard-switching FET converter operating at 100 kHz for a single-phase, the proposed converter shows a fairly good improvements in efficiency and reducing harmonics due to the soft-switching effect.

#### References

- [1] R.F. Brewster and A.H. Barret, "Three-phase AC to DC voltage converter with power line harmonic current reduction," U.S. Patent 4 143 414, Mar. 6, 1979.

- [2] M.J. Kocher and R.L. Steigerwald, "An AC to DC converter with high quality input waveforms." *IEEE Trans. Power Electronics*, pp. 63-75, 1982.

- [3] S. Manias and P.D. Ziogas, "A novel sinewave in AC to DC converter with high-frequency transformer isolation," *IEEE Trans. Ind. Electron.*, vol. IE-32, no. 4, pp. 430-438, Nov. 1985.

- [4] J.A. Sabate, V. Vlatkovish, R.B. Ridly, F.C. Lee and B.H. Cho, "Design considerations for high-

- voltage high-power full-bridge zero-voltageswitched PWM converter," *Proc. of IEEE APEC* 1990, pp. 275-284.

- [5] J.G. Cho, J.A. Sabate, G. Hua and F.C. Lee, "Zero-voltage and zero-current switching full-bridge PWM converter for high power applications," *Proc. of IEEE PESC 1994*, pp. 102-108.

### Appendix

#### \* Schematics Netlist \*

| R_R15 S                  | \$N_0001 HS3_Isine 750k |  |  |

|--------------------------|-------------------------|--|--|

| R_R16                    | HS3_rampcom 0 170k      |  |  |

| R_R17                    | HS3_mult 0 210k         |  |  |

| D_HS3_D3                 | \$N_0014 0 Dbreak       |  |  |

| V_HS3_HS2_V2             | \$N_0030 0 5V           |  |  |

| X_H\$3_HS2_U2            | \$N_0030 vdc \$N_0031   |  |  |

| \$N_0032 HS3_eaout uA741 |                         |  |  |

| D_HS3_HS2_D3             | HS3_eaout vdc Dbreak    |  |  |

| V_HS3_HS2_V3             | \$N_0031 0 8V           |  |  |

| V_H\$3_H\$2_V6           | \$N_0032 0              |  |  |

| V-D_HS3_D4               | \$N_0015 0 Dbreak       |  |  |

| V_H\$3_V1                | \$N_0016 0 9V           |  |  |

| V_H\$3_V9                | \$N_0017 0 15V          |  |  |

| R_HS3_R3                 | \$N_0017 HS3_out 750    |  |  |

| V_HS3_V7                 | \$N_0018 0 5V           |  |  |

| R_HS3_R2                 | \$N_0019 H\$3_clock 1k  |  |  |

| V_HS3_V8                 | SN_0020 0 5V            |  |  |

| V_HS3_V4                 | \$N_0021 0 5V           |  |  |

| Q_HS3_Q1                                            |                                         | + TANH((1k)*(V(\$N_0002)-(((30)+(0))/2))/((((30)- |                                  |

|-----------------------------------------------------|-----------------------------------------|---------------------------------------------------|----------------------------------|

| HS3_Iramp Q2N2222                                   |                                         | (0))/2))))}                                       | 731 0020 0 MALLIE                |

| G_HS3_ABM311                                        | \$N_0016 HS3_mult                       | E_SLIMIT2                                         | _                                |

| VALUE { (V(\$N_00                                   | 22)*                                    | {(((30)+(0))/2) + ((((30)-(0))/2) *               |                                  |

| + V(\$N_0023)                                       |                                         | + TANH((1k)*(V(\$N_0003)-(((30)+(0))/2))/((((30)- |                                  |

| + -V(\$N_0024)/2)                                   | }                                       | (0))/2))))}                                       |                                  |

| H_HS3_H2                                            | \$N_0022 0 VH_HS3_H2 1                  | R_H\$6_R1                                         | 0 0 1meg                         |

| VH_HS3_H2                                           | HS3_Ierr \$N_0015 0V                    | F_HS6_F1                                          | \$N_0038 0 VF_HS6_F1 1           |

| H_HS3_H1                                            | \$N_0023 0 VH_H\$3_H1 1                 | VF_HS6_F1                                         | \$N_0037 pfc 0V                  |

| VH_HS3_HI                                           | HS3_Isine \$N_0014 0V                   | E_H\$6_E1                                         | \$N_0037 0 \$N_0038 0 1          |

| H_HS3_H3                                            | \$N_0024 0 VH_H\$3_H3 1                 | R_HS5_R1                                          | 00 lmeg                          |

| VH_HS3_H3                                           | HS3_Iramp HS3_rampcom                   | F_HS5_F1                                          | \$N_0040 0 VF_H\$5_F1 1          |

| 0V                                                  |                                         | VF_HS5_F1                                         | \$N_0039 zvt 0V                  |

| X_H\$3_U9A                                          | \$N_0035 \$N_0025                       | E_HS5_E1                                          | \$N_0039 0 \$N_0040 0 1          |

| \$N_0026 \$G_DPWR                                   | \$G_DGND 7428 PARAMS:                   | E_E1                                              | \$N_0002 0 TABLE { V(H\$3_clock, |

| + IO_LEVEL=0 MNTYMXDLY=0                            |                                         | 0) }                                              |                                  |

| X_HS3_U7A                                           | \$N_0035 \$N_0026                       | + ( (-15,0) (-0.0                                 | 01,0) (1,0) (1.1,30) (15,30) )   |

| \$N_0027 \$G_DPWR                                   | \$G_DGND 7428 PARAMS:                   | E_E2                                              | \$N_0003 0 TABLE { V(HS3_out.    |

| + IO_LEVEL=0 MNTYMXDLY=0                            |                                         | 0) }                                              |                                  |

| Q_HS3_Q3                                            | \$N_0020 \$N_0035 \$N_0019              | + ( (-15,0) (-0.0                                 | 01,0) (1.0,0) (1.1,30) (15,30) ) |

| QbreakN                                             | -                                       | R_R12                                             | \$N_0005 \$N_0004 178k           |

| X_HS3_U8A                                           | \$N_0027 HS3_out                        | R_R14                                             | \$N_0004 vdc 178k                |

| \$G_DPWR \$G_DGND 7407 PARAMS:                      |                                         | D_D8                                              | \$N_0042 \$N_0005 Dbreak         |

| + IO LEVEL=0 MNTYMXDLY=0                            |                                         | D_D9                                              | 0 \$N_0006 Dbreak                |

| X HS3_U10A                                          | \$N_0026 \$N_0028                       | R_R13                                             | vdc 0 4.75k                      |

| \$N 0025 \$G DPWR \$G DGND 7428 PARAMS:             |                                         | D_D6                                              | 0 \$N 0007 Dbreak                |

| + IO LEVEL=0 MNTYMXDLY=0                            |                                         | C_C7                                              | \$N_0008 \$N_0009 0.68uF         |

| V_HS3_HS1_V2                                        | \$N 0035 0                              | V_V6                                              | \$N 0010 \$N 0009                |

| +PULSE 0 5 {1/100kHz-lu} 10n 10n {1u}               |                                         |                                                   | *sqrt(2.)} 60Hz 0 0 0            |

| {1/100kHz}                                          | 12, 12, 12, 12, 12, 12, 12, 12, 12, 12, | D_D10                                             | \$N_0011 \$N_0001 Dbreak         |

| V_HS3_HS1_V1                                        | \$N_0036 0                              | D_D11                                             | \$N_0008 \$N_0001 Dbreak         |

|                                                     | <del>-</del>                            | D_D12                                             | 0 \$N 0011 Dbreak                |

| +PULSE 0 3.5 0 {1/100kHz-lu} {lu} 10n<br>{1/100kHz} |                                         | D_D12<br>D_D13                                    | 0 \$N 0008 Dbreak                |

| •                                                   | HS3_eaout HS3_Ierr 10k                  | R_R25                                             | \$N_0009 0 1meg                  |

| E_HS3_SUM1                                          | \$N_0029 0 VALUE                        | L_L5                                              | \$N_0009 \$N_0011 15uH IC=3      |

| _ <del>_</del>                                      |                                         | C_C4                                              | \$N_0005 0 680uF IC=350V         |

| {V(\$N_0018)+V(HS3_mult)}                           |                                         | -                                                 |                                  |

| E_HS3_E1                                            | \$N_0028 0 TABLE { V(i.                 | M_M2                                              | \$N_0007 zvt 0 0 IRF840          |

| \$N_0029) }                                         | \ (0.0\ (0.001 E) \ (15.5\ \)           | H_HS7_H1                                          | \$N_0043 0 VH_H\$7_H1 1          |

| + ( (-15.0) (-0.001,0) (0.0) (0.001, 5) (15,5) )    |                                         | VH_HS7_HI                                         | \$N_0041 \$N_0042 0V             |

| R_R21 HS3_clock 0 10k                               |                                         | X_HS7_X1                                          | \$N_0044 0 \$N_0045              |

| E_SLIMIT1 \$N_0040 0 VALUE                          |                                         | \$N_0046 \$N_0041 ZX                              |                                  |

| {(((30)+(0))/2) + (((                               | (30)-(0))/2) *                          | L_HS7_L2                                          | \$N_0045 0 {{Ls}}}               |

```

E_HS7_E1

$N_0047 0 TABLE

{ V($N_0043, 0) }

+ ( (-0.3.0.0),(-0.29.0.1), (0, 1), (0.29.1), (0.3.0.1) )

$N 0044 0

E_HS7_LOPASS1

CHEBYSHEV {V($N 0047)} LP (1megHz

5megHz) 1dB

+ 50dB

$N_0050 0 VH_HS8_H1 1

H HS8 HI

VH HS8 H1

$N 0048 $N 0049 0V

X_HS8_X1

$N_0051 0 $N_0052

$N 0053 $N 0048 ZX

L HS8 L2

$N_0052 0 {{Ls}}}

E_HS8_E1

$N_0054 0 TABLE

{ V($N_0050, 0) }

+ ( (-0.3,0.0),(-0.29,0.1), (0, 1), (0.29,1), (0.3,0.1) )

E HS8 LOPASS1

$N 00510

CHEBYSHEV {V($N 0054)} LP (1megHz

5megHz) 1dB

+ 50dB

C_C8

0 $N_0012 1n

R R27

$N 0012 i 33k

0 $N_0012 100

R_R28

C C9

$N 0012 i 47n

F_F1

0 $N_0012 VF_F1 0.005

VF_F1

$N_0013 $N_0053 0V

R RI

$N 00050 144

D D5

$N_0042 $N_0007 Dbreak

M M3

$N 0006 pfc 0 0 IRF840

C C2

$N_0001 0 0.68uF IC=0

C C6

vdc HS3 eaout 0.47u

R R19

zvt 0

1meg

R R22

pfc 0

1meg

L L2

$N_0001 $N_0013

550uH IC=3.5A

V V5

$N 0049 $N 0006 DC

V0

L L3

$N 0053 $N 0046

\{-2.*Ls+11u\}

R_R26

$N_0010 $N_0008

0.01

D D7

$N_0049 $N_0005

Dbreak

```