'88 추계학술대회

'88 - L - 2

Design of CMOS OTA-C Integrator with a Wide Linear Input Range

OYun Tae Shin\*, Joung Cheol Ahn\*, Kyoo Jae Shin\*\*, Dong Yong Kim\*\*\*

\* Dept. of Electrical Engineering, Chonbuk National University

\*\* The Navy Discipline Headquaters

\*\*\* Prof. in Dept. of Electrical Engineering, Chonbuk National University

### ABSTRACT

A n-well CMOS Operational Transconductance Amplifier -C(OTA-C) integrator with a wide linear input range is designed. The circuit designed has superior linearity of input voltage range compared with the conventional source-coupled pair OTA. The OTA developed in this paper is versatile in application: diverse applications are in the fields of linear amplifiers, continuous-time filters, gain control circuits, and analog multipliers, etc...

#### 1. INTRODUCTION

Recently, novel CMOS circuits, Switched-Capacitor Filter(SCF), continuous-time MOSFET-Capacitor(MOSFET-C) filter, which can perform analog functions and which can also share the same chip with the digital circuitry have been developed.

The SCF[1,2], which is realized by a combination of switches and capacitors instead of resistor in active RC filter are now widely used for their precision real-rization in MOS technology. However, the SCF has inherent problems due to the sampled-data system: the dynamic range of SCF is always reduced by clock feedthrough noise and by the aliasing of the wide-band Op Amp and switch noise into the passbands. Also SCF usually needs antialiasing filtering at their inputs, and smoothing filtering at their outputs. Moreover, the switches and the associated clock lines can make the layout of the circuit complicated.

To overcome these problems, M.Banu and Y.Tsividis[3] have proposed MOSFET-C filter using the continuous-time fully-balanced structure for cancellation of nonlinear resistance. And I.S.Han and S.B.Park[4] have suggested another MOSFET-C filter design method by voltage-cont-

rolled linear resistor realization using simple connection of two MOSFETs. In the MOSFET-C techniques, problems due to the capacitor switching are removed, but the circuits are still required many extra components, as it were, the resistors in active RC filters. These problems can be solved by continuous-time active C filters which is eliminated resistors.

In this paper, therefore, CMOS Operational Transconductance Amplifier-Capacitor (OTA-C) integrator with a wide linear input range as building block of active C filter is realized.

# 2. LINEARIZED DIFFERENTIAL INPUT STAGE

All MOSFETs are assumed to be enhancement-mode types biased in saturation with substrates connected to their respective sources. Thus body effect is ignored and the transistor behavior is approximated by the relation

$$I_{B} = k(V_{GS} - V_{T})^{2}$$

(2.1)

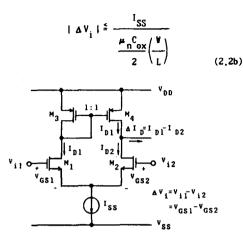

where V $_{\rm I}$  is the threshold voltage, k=(1/2)  $\mu$ C $_{\rm ox}$ (V/L) is the transconductance parameter, V and L are width and length of the channel,  $\mu$  is the effective surface carrier mobility and C $_{\rm ox}$  is the gate oxide capacitance per unit area. If the drain currents as shown in Fig. 2.1 are differenced using a p-channel current mirror of unity-gain to form a singled ended current output  $\Delta$ I $_{\rm D}$ , assuming matched devices, the relation of  $\Delta$ I $_{\rm D}$  and difference input voltage  $\Delta$ V $_{\rm i}$  is

$$\Delta I_{D} = 2 \frac{\mu_{n}^{C}_{ox}}{2} \left(\frac{V}{L}\right) (V_{GS1} + V_{GS2} - 2V_{T}) \frac{V_{GS1} - V_{GS2}}{2} (2.2a)$$

$$= \frac{\mu_{n}^{C}_{ox}}{2} \left(\frac{V}{L}\right) \Delta V_{i} / \frac{2I_{SS}}{\mu_{n}^{C}_{ox}} \left(\frac{V}{L}\right) + \Delta V_{i}^{2} :$$

Fig. 2.1 Source-coupled pair with current sink  $I_{\overline{SS}}$  and load

This indicates that the linear range of source-coupled pair is limited because the difference output current is nonlinear function of difference input voltage.

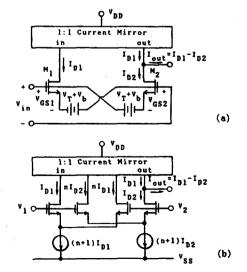

To increase input linear range, if the last term in Eq.(2.2a) equals to the applied differential input voltage  $V_{in}$  and the term  $(V_{GS1}^{+}V_{GS2}^{-}2V_{T}^{-})$  equals to a constant voltage, say  $2V_{b}^{-}$ , as shown in Fig. 2.2(a), Eq.(2.2) results

$$I_{out} = 4kV_bV_{in}. \qquad (2.3)$$

Thus this configuration, exhibits a perfectly linear transconductance of value  $g_a=4kV_h$

Fig. 2.2 Linearized differential input: (a) principle, (b) cross-coupled pair implemented by source  $V_{T}^{+V}_{h}$

For implementing the source  $(V_T + V_b)$ , two additional n-channel transistor  $M_3$  and  $M_4$  biased by constant currents, i.e., cross-coupled pair, can be used as in Fig. 2.2(b). Here, for obtaining reasonable voltage source with low source impedance, these devices must be wide[5].

## 3. DESIGN OF CMOS OTA-C INTEGRATOR

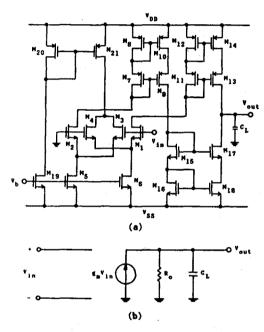

Fig. 3.1(a) shows the CMOS OTA-C integrator that can be used as basic building block of active C filter realization.

Fig. 3.1 CMOS OTA-C integrator: (a) complete schematic, (b) small signal equivalent circuit of (a).

The devices  ${\rm M_1-M_4}$  are cross-coupled pair for linearizing the input range, and  ${\rm M_5-M_{21}}$  are current mirrors as loads. It should be noted that cascode current mirrors are used for large dc open-loop gain. Assuming unity-gain current mirror, output current is given by Eq.(2.3) and transconductance of cross-coupled pair is adjustable by control voltage  ${\rm V_b}$ . Small signal equivalent circuit of Fig. 3.1(a) is shown in Fig.3.1(b), and the device dimensions are shown in Table 3.1. Then, output resistance is given by

$$R_{\text{out}} = \frac{(r_{\text{ds}13} + r_{\text{ds}14} + r_{\text{ds}13} \cdot r_{\text{ds}14} \cdot g_{\text{m}13})}{(r_{\text{ds}17} + r_{\text{ds}18} + r_{\text{ds}17} \cdot r_{\text{ds}18} \cdot g_{\text{m}17})}$$

(2.4)

where  $r_{ds}$  is the drain resistance,  $g_{m}$  is the transconductance which can be represented by Voltage-Controlled

Current Sources(VCCSs). And voltage gain is given by

$$A_{v} = g_{m} R_{out}. \qquad (2.5)$$

Table 3.1 Device dimensions

| Devices                           | ٧/L[ μ m] |

|-----------------------------------|-----------|

| M <sub>1.</sub> M <sub>2</sub>    | 3/3       |

| M <sub>3</sub> , M <sub>4</sub>   | 60/3      |

| M <sub>5</sub> , M <sub>6</sub>   | 3/6       |

| M <sub>7</sub> -M <sub>14</sub>   | 10/3      |

| M <sub>15</sub> -M <sub>18</sub>  | 3/152     |

| M <sub>19</sub>                   | 20/17     |

| M <sub>20</sub> , M <sub>21</sub> | 24/3      |

In Fig. 3.1(b), it should be noted that output current,  $g_{\mathbf{n}}V_{\mathbf{in}}$  directly flows into capacitive load because the output resistance are very large(approximatly 240 Ma). From Fig. 3.1(b), output voltage and do output voltage is given by

$$V_{\text{out}} = \frac{g_{\text{m}}V_{\text{in}}}{g_{\text{out}} + sC_{\text{I}}}$$

(2.6)

$$V_{\text{out}} = \frac{g_{\text{N}}V_{\text{in}}}{g_{\text{out}}^{+\text{sC}_{\text{L}}}},$$

$$V_{\text{out}} = \frac{g_{\text{N}}V_{\text{in}}}{g_{\text{out}}}$$

(2.6)

respectively. Thus, 3dB frequency  $f_{c}$  is given by

$$f_c = \frac{g_{out}}{2\pi c_t}$$

(2.8)

## 4. SPICE 2G. SIMULATION RESULTS

Table 4.1 CMOS OTA-C integrator performance characteristics[ $V_{DD} = -V_{SS} = 5V$ ,  $V_{b} = -3V$ ,  $C_{L} = 1pF$ ]

| Design Parameters            | Values         |

|------------------------------|----------------|

| Low-Frequency Open-Loop Gain | 76.04 dB       |

| Unity Gain Frequency         | 2 MHz          |

| Slew Rate                    | 20/ <b>#</b> s |

| CMRR                         | 92.12 dB(1Hz)  |

|                              | 43,46 dB(2MHz) |

| PSRR: V <sub>DD</sub>        | 113,83 dB(1Hz) |

|                              | 41.92 dB(2MHz) |

| v <sub>ss</sub>              | 71.82 dB(1Hz)  |

|                              | 19.34 dB(2MHz) |

| Phase Margin                 | 84°            |

| Input Offset Voltage         | 0,9mV          |

| Power Dissipation            | 0.864mW        |

| Output Resistance            | 242,6MΩ        |

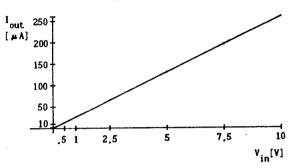

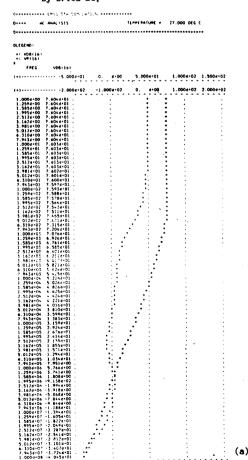

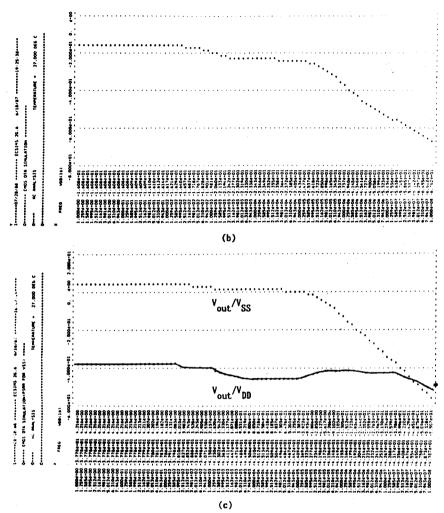

The frequency characteristics, common-mode gain for CMRR, and Vout/VDD and Vout/VSS for PSRR of complete CMOS OTA-C integrator when capacitive load is 1pF, is shown in Fig. 4.1 under dc bias condition, VDD=-VSS\*5V and  $V_{\rm h}$ =-3V by SPICE 2G, simulation. The performance characteristics are summarized in Table 4.1. Also, the relation of output current and input voltage is indicated in Fig. 4.2. Here, it should be noted that the output current is perfectly proportional to the input voltage and is a few microamps.

Fig. 4.2 Measured output current(transconductance) by SPICE 2G.

Fig. 4.1 OTA-C characteristics [ $V_{DD}^{=-}V_{SS}^{=-5V}$ ,  $V_b^{=-3V}$ ,  $C_L^{=1pF}$ ]: (a) frequency characteristics, (b) common-mode gain for CMRR, (c)  $V_{out}/V_{DD}$  and  $V_{out}/V_{SS}$  for PSRR. REFERENCES

# 5. CONCLUSION

In this paper, a n-well CMOS OTA-C integrator with a wide linear input range for application in continuoustime active C filter has been designed. The circuit has been used cross-coupled pair and cascode current mirror to provide accurate controllable transconductance over a larger range than that possible with a source-coupled pair and large output resistance, respectively.

From the performance characteristics, OTA-C integrator is suitable for low power high-frequency signal processing[several MHz] as well as voice-frequency signal processing as the appropriate active C filters satisfied with transfer functions instead of SC and MOSFET-C filters.

- [1] P.E.Allen and A.Sanchez-Sinencio, Switched Capacitor Circuits, Van Nostrand Reinhold, N.Y., 1984.

- [2] R.Gregorian and G.C.Temes, Analog MOS Integrated Circuits for Signal Processing, John Wiley & Sons, N.Y., 1986.

- [3] M.Banu and T.Tsividis, "Fully Integrated Active RC Filters in MOS Technology", IEEE J.Solid-State Circuits, vol.SC-18, no.6, pp.644-651, Dec. 1983.

- [4] I.S.Han and S.B.Park, "Voltage-Controlled Linear Resistor by Two MOS Transistors and Its Application to Active RC Filter MOS Integration", Proc. IEEE, vol.72, no.11, pp.1655-1657, Nov. 1984.

- [5] A.Nedungadi and T.R.Viswanathan, "Design of Linear CMOS Transconductance Elements", IEEE Trans. Circuits and Systems, vol.CAS-31, no.10, pp.891-894, Oct. 1984.