# Topological analysis of DC motor driving by John's Chopper Circuit

## WOW CHUNG YUN, HWANG HEE YEUNG

### College of Eng. Secul National University

### ABSTRACT :

The puropose of this paper is to develop an efficient model for the analysis of a John's Chopper Circuit.

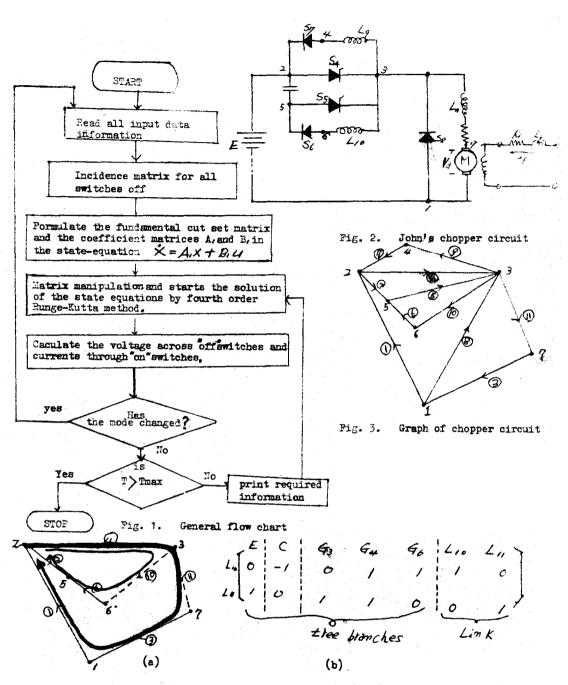

In the John's Chopper Circuit analysis, the open branches are removed from the associated graph to formulate the modified incidence matrix. An alogorithm for the generation of a modified proper tree and fundamental cut set matrix from a network graph is developed, which utilizes much less computer stroage space and computation time compared to the classical methods.

#### THURODUCTION

The chopper controlled DC separately and series excited motors are now widely used in traction and many other industrial applications. In motor DC drives, the classical motor-generator set has been replaced by a thyristorized power convertor which provides faster response at a lower total cost.

In digital computation of thyristors and diodes are replaced by switches and their switchings are determined by their voltages, currents and gate signals.

The on switch is represented by a series combination of voltage and a small resistance, while the off switch is represented by very large resistence.

Setwork topology makes use of the formulation of the state equations in the computer. The purpose of the present paper is to make use of network topology for the formulation of state equations in the thyristor circuits with the main object of eliminating the problem of widely varing time constants and a generalized digital simulation method for the analysis of chopper fed DC motor.

The important features of this method are

- 1) It can be used for any chopper circuits.

Only the circuit connection and the parameters of circuit elements are needed as the input data.

- 2) It does not need the prior knowledge of different modes of operation of the chopper circuit and derivation of the relevant equations.

The program itself enables one to determine the node sequence and derive and solve the

system equations automatically.

- 3) For minimizing computer time in forming the state equations, the "off" switch can be easily removed by Revankar's approach.

- 4) The Runge-Kutta methods used in this paper are based on fourth-order Taylor approximation.

- II. Topological partitioning of the thyristor circuits

It is convenient to partition the fundamental loop and cut-set matrices according to the nature of network elements.

The order of numbering the network branches is E(voltage source), C(capacitance), R(resistance), Switches(SCR, Diode), L(inductance), and J(Current source). In the graph of the thyristor circuit, all the switching device branches are oriented from anode to cathode to represent the possible current flow direction.

### III. Normal Tree

Define a "normal tree" as a having as twigs all of the independent voltage sources, the maximum possible number of capacitors, the minimum possible number of inductors, and none of the independent current sources.

The algorithmm for formulation the modified complete incidence matrix is follows:

- (a) In the columns of An corresponding to the off-switches replace all nonzero entries by zeros.

- (b) Check up the rows for one nonzero entry. If such a row exist, then replace its nonzero entry by a zero.

- (c) Check the columns for one nonzero entry. If such a column exists, then replace its nonzero entry by a zero.

- (d) Repeat steps (b) and (c) till none of the rows and column contain one nonzero entry.

- (e) Formulate Asm by eliminating the rows and columns containing all zeros.

IV. Formulation of state equation and elementary propeties Hormal form of the state equation is

$$\frac{dx}{dt} = A_1X + B_1U$$

## where X is the state vector

U is the input vector

and  $A_1$  and  $B_2$  are the matrices evaluated on basis of cut set submatrix  $Q_1$

Switching-device voltage and current relations On-switching branch current are given by

The fundamental loop matrix B for this choice of normal tree is illustrated in Fig. 4 (b). Where the dashed lines shows the partitioning of the submetrix F.

: link elastance

C: tree branch capcitances

3 : link resistance

G: " conductances

L : link inductance

reciprocal inductances

symmetric admittance matrix : 🕍 current transfer matrix : 🦊 impedence matrix : 🙎

voltage transfer matrix : - 4

# VI. Conclusion

The described program can make fast computational time by Revankar's method using the modified incidence matrix obtained by removing "off" switch.

### VII. References

- Benjamin C. KUO, Automatic control system, pp 220-225.

- G.N. Revankar, "Topological approach to thyristor circuit analysis," proceedings IEE, Vol 120, pp 1403-1405, November 1973.

- 3. Fitzgerald, Kingsley Kusko, Electric machinery, pp 442-448.

- 4. Franklin KUO. Computer Applications in Electrical Engineering Series. pp 371-395.

- 5. Charles A. Dessor & Irnests, Kuh "BASIC CIRCUIT THEORY" pp 477-521.

- E.S. KUH. and R.A. ROHRER, "The state variable Approach to Network Analysis," PROCEEDINGS OF IEEE, 53: 672-686. 1965.

VIII Appendix

$$\begin{array}{lll}

\mathbf{J} \equiv F_{RC} R^{-1} F_{RC}. & \mathbf{J} \equiv F_{LC} - F_{RC} R^{-1} F_{RG} R_{L} F_{LG}. & \mathbf{J} \equiv F_{RC} R^{-1} F_{RC} R_{LG}. & \mathbf{J} \equiv F_{RC} R_{LG} R_{LG}. & \mathbf{J} \equiv F_{RC} R_{LG}. & \mathbf$$

Fig. 4.(a) Normal tree corresponding to off-switch branches 5,7 and 8.

(b)fundamental loop matrix B.