## Pabrication of 1<sup>2</sup>L by New Process and Its Chracteristics

Chul-Ei Han Choong-Ka Kim

Department of Electrical ocience Korea Advanced Institute of Science

Since its introduction in 1972, integrated injection logic(I<sup>2</sup>L), or merged transistor logic(NTL), has received the close attention ISI researchers, due to its high packing density, excellent speed power product, low fabrication cost, and compatibility with analog circuits.

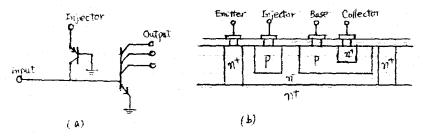

The basic building block of an I<sup>2</sup> is the single-input multioutput inverter shown schematically in Fig. -a. The standard I<sup>2</sup> I

gate structure, as shown in Fig. -c, is fabricated by diffusing

two adjacent p-type regions into the n-t, pe wafer, then diffusing

n<sup>+</sup>-regions into one of the p-type regions. The structure of basic

I<sup>2</sup> I, as shown in Fig. 1-b, is very simple, due to merged transisto

structure, and results in few metal interconnections. The collecto

is the top n<sup>+</sup>-diffused region and the common emitter is the n<sup>+</sup>substrate. The p-regions form the emitter and collector of the

many transistor.

initially I<sup>2</sup>L circuits were fabricated using standard bipolar diffusion technique and resulted in impressive performance chracteristics. However, the standard I<sup>2</sup>L structure has some disadvantages such as low upward current gain and low speed operation.

A m diffied npm transistor structure with double base has been proposed to improve the speed and to increase the upward current gain. However, the modified structure requires different doping in the extrinsic base region from the intrinsic region and the complexity of the process is increased[0]. A high performance I<sup>2</sup>L process using only five masks was proposed by Seo [2], which is expected to improve the performances of I<sup>2</sup>L such as current gain of the pap and npm transistor and speed power product.

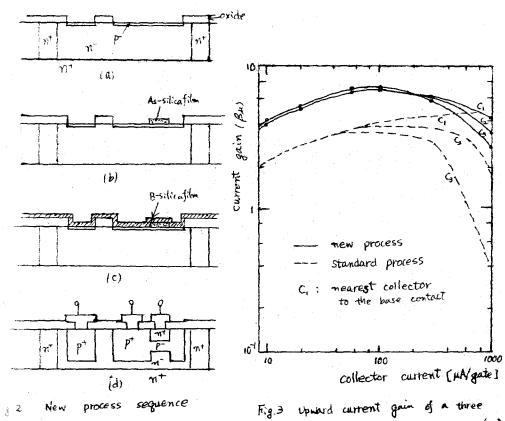

The new fabrication process uses spin-on source as the diffusion source. The  $I^2L$  structure using the new process is shown in Fig.2-d. Fig.2 shows the new fabrication process. The fabrication sequence is listed below.

- 1) Diffuse heavily doped n collar on n/n silicon wafer to minimize extraneous base current of the npn transistor.

- Boron predeposition in the injector and base region. (Fig. 2-a)

- 3) Arsenosilicafilm coating and photomasking to remove the arsenosilicafilm except collector regions. (Fig.2-b)

- 4) Borosilicafilm coating. (Fig. 2-c)

- 5) Simultaneous diffusion of boron and arsenic and removing the spin-on sources. Here, the arsenosilicafilm acts as a masking layer against the borosilicafilm during diffusion.

- 6) Reoxidation, contact and metallization.

I<sup>2</sup>L test devices including 13-stage ring oscillator have been fabricated by the new process proposed by Seo. As a starting material, silicon (111) wafers uniformly doped n<sup>+</sup> with a 6.5 mm n<sup>-</sup>epitaxial layer of concentration 10<sup>16</sup>cm<sup>-3</sup> have been used.

An upward npn current gain of 8, a speed power product of 3.5 pJ and a minimum propagation delay time of 50ns with standard device breakdowns(BV<sub>CRO</sub>) of 22 wolts have been obtained.

Fig. 3 shows the upward current gain versus collector currents of a three collector I<sup>2</sup>L gate. Compared with others (1)(3), improvement in the upward current gain by a factor of 2 is achieved and the upward current gain fall-off of collectors farther away from the base contact due to base resistance at high current range is reduced. And the test results show that the current gain control of the npn transistors can be easily achieved by varying the sheet resistance in the intrinsic base region during boron predeposition step.

## References

- (1) J.C.Plunkett, "Inverse Current Gain Improvement of Bipolar Transistors by Double-base Diffusion," IEEE Trans. Electron Devices, Vol. ED-24, pp1269-1270, Oct. 1977.

- (2) K.S.Seo, "A Study on the Integrated Injection Logic-Analysis and New Fabrication Process, "M.S.Thesis of KAIS, 1978.

- (3) J.L.Saltich, et al, "Processing technology and AC/DC Chracteristics of Linear Compatible I<sup>2</sup>L," IEEE J.Solid-State Circuits, Vol.SC-11, Aug. 1976.

Figl. (a) Schematic diagram of an I'L gate (b) Crosssectional view of a standard unit cell.

collector I'L. (\*: thim epi-water)